技术摘要:

本发明公开了一种半导体结构,包括衬底,所述衬底上有一鳍状结构,浅沟槽隔离结构,位于所述衬底中,其中所述浅沟槽隔离结构具有一阶梯状顶面,并具有第一顶面以及高于所述第一顶面的第二顶面,以及一栅极结构,跨越部分所述浅沟槽隔离结构以及部分所述鳍状结构,其中 全部

背景技术:

由于半导体组件朝向高密度化发展,单元面积内的组件尺寸不断减小。半导体组 件因其尺寸小,功能多和/或制造成本低而广泛用于电子工业。半导体组件分为储存逻辑数 据的半导体组件,操作、处理逻辑数据操作的半导体逻辑组件,或是同时具有半导体储存组 件的功能和半导体逻辑组件和/或其他半导体组件功能的混合半导体组件。 近年来,随着场效晶体管(field effect transistors,FETs)组件尺寸持续地缩 小,习知平面式(planar)场效晶体管组件之发展已面临制程上之极限。为了克服制程限制, 以非平面(non-planar)之场效晶体管组件,例如鳍状场效晶体管(fin field effect transistor,Fin FET)组件来取代平面晶体管组件已成为目前之主流发展趋势。由于鳍状 场效晶体管组件的立体结构可增加闸极与鳍状结构的接触面积,因此,可进一步增加栅极 对于载子信道区域的控制,从而降低小尺寸组件面临的漏极引发能带降低(drain induced barrier lowering,DIBL)效应,并可以抑制短通道效应(short channel effect,SCE)。再 者,由于鳍状场效晶体管组件在同样的栅极长度下会具有更宽的通道宽度,因而可获得加 倍的漏极驱动电流。甚而,晶体管组件的临界电压(threshold voltage)亦可藉由调整栅极 的功函数而加以调控。

技术实现要素:

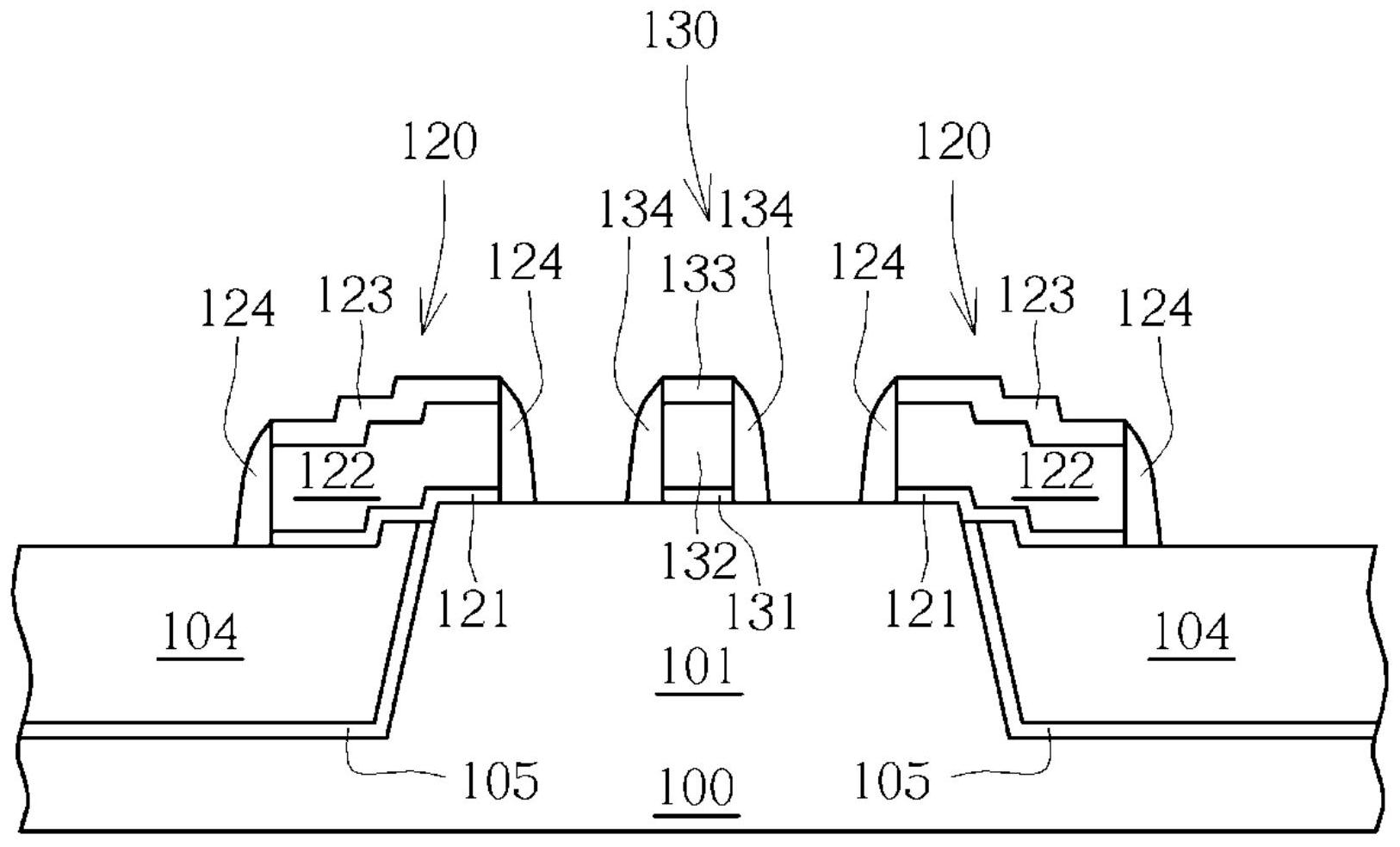

本发明公开了一种半导体结构,包括衬底,上述衬底上有一鳍状结构,浅沟槽隔离 结构,位于上述衬底中,其中上述浅沟槽隔离结构具有一阶梯状顶面,并具有第一顶面以及 高于上述第一顶面的第二顶面,以及一栅极结构,跨越部分上述浅沟槽隔离结构以及部分 上述鳍状结构,其中上述栅极结构具有一阶梯状的底面。 可选地,其中上述第二顶面低于上述鳍状结构的顶面。 可选地,其中上述栅极结构包含有由下而上依序堆栈的衬垫层、导电层以及掩膜 层。 可选地,其中从剖面图来看,上述衬垫层具有阶梯状的剖面结构,且上述阶梯状的 剖面结构具有三个不同水平高度。 可选地,其中上述导电层的底面低于上述鳍状结构的顶面。 可选地,其中上述栅结构的硬掩膜层包含有阶梯状顶面。 可选地,其中上述栅极结构的最低底面与上述浅沟槽隔离结构的第一顶面齐平。 可选地,更包含有第二栅极结构,位于上述衬底上,其中上述第二栅极结构不位于 上述浅沟槽隔离结构上方。 可选地,其中上述第二栅极结构具有平坦顶面。 3 CN 111584638 A 说 明 书 2/5 页 本发明的特征在于,调整制作浅沟槽隔离结构时的蚀刻参数,形成具有阶梯状剖 面结构的浅沟槽隔离结构。申请人发现该阶梯状的浅沟槽隔离结构具有更高的结构强度, 且易于在浅沟槽隔离结构与鳍状结构的边界上形成虚置栅极结构。后续形成虚置栅极结构 于阶梯状顶面时,可以保护鳍状结构本身以及栅极结构,提高组件的质量。 附图说明 构成本发明的一部分的说明书附图用来提供对本发明的进一步理解,本发明的示 意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中: 图1至图3绘示本发明优选实施例中形成半导体结构的步骤示意图。 图4绘示本发明另一优选实施例的半导体结构示意图。 其中,上述附图包括以下附图标记: 100衬底 101鳍状结构 102沟渠 104绝缘层 105衬垫层 106浅沟槽隔离结构 110图案化屏蔽 111氧化硅层 112氮化硅层 113氧化硅层 120虚置栅极结构 121栅极电介质层 122栅极导电层 123掩膜层 124间隙壁 130栅极结构 131栅极电介质层 132栅极导电层 133掩膜层 134间隙壁 S1顶面 S2顶面 S3顶面