技术摘要:

本发明公开了一种集成叠层母排的双面水冷SiC半桥模块封装结构。所述封装结构包括主体结构、外部连接结构以及散热装置,外部连接结构和散热装置均与主体结构相连。所述主体结构包括上DBC、下DBC、SiC半导体芯片、垫片。所述外部连接结构包括叠层母排和交流母排,叠层母 全部

背景技术:

功率半导体器件是电力电子变流器的核心部件。近年来,随着电力电子技术在新 能源发电和电动汽车等领域的快速发展以及SiC等宽禁带半导体的开发,对功率半导体器 件也提出了新的需求。 虽然SiC等宽禁带半导体比Si基半导体具有更高的工作温度、更高的击穿电压强 度、更高的热导率以及更高的开关频率。然而,将基于Si功率器件的传统的封装技术用来对 宽禁带半导体功率器件进行封装时,会带来两个较大的问题。一是传统封装技术采用引线 键合来实现结构中复杂的内部互联,这会带来较大的寄生电感,在功率半导体器件关断时, 较大寄生电感中存储的能量会造成电压尖峰和振荡,并可能增加损耗,随着近年来功率半 导体器件开关速度越来越快,封装的寄生电感问题更为突出。因此为了保障功率器件和电 力电子系统的性能和安全运行,在功率模块封装设计时需注意减小封装寄生电感。二是传 统封装技术的散热方式多为单面散热,因此,散热效率差。而SiC器件可以工作在更高的温 度下,因此在散热方面具有更高的要求,若没有高效的散热方式,会影响模块可靠性。 因此,开发具有低寄生电感和高效散热方式的封装结构已经成为研究的热点问 题,这既有学术论文对此做了深入的理论分析,也有实际应用的工程方法,如发明申请专利 《双面散热IPM混合模块的封装结构及加工工艺》(CN109920785A)和《带固定装置双面水冷 的半导体器件三维堆叠封装结构》(CN103367278A)。 中国发明专利申请公开说明书公开的《双面散热IPM混合模块的封装结构及加工 工艺》,以上下双基板且芯片倒装的封装形式,将IGBT芯片的发射极和SBD芯片的阳极通过 覆铜陶瓷板连接到引线框架,减少键合引线,提升模块可靠性;再以纳米银互连层替代芯片 与基板之间的焊料层,有助于发挥SiC材料的高温特性,同时提高热量从芯片到基板的纵向 传导能力,从而降低IPM混合模块的最高温度,提升模块使用寿命。但是,该结构存在以下不 足: 1、该结构并未考虑降低功率端子方法,而封装结构大部分电感来自于功率端子: 2、该结构并不是使用水冷散热,无法满足大功率器件的要求 中国发明专利申请公开说明书书公开的《带固定装置双面水冷的半导体器件三维 堆叠封装结构》,实现了半导体器件的立体封装,无引线键合,降低引线键合所产生的线路 电阻和自身电感,采用双面水冷散热,具有体积小,可集成的功率大,散热系数大。同时,每 个叠压板可以封装任意个数的以及尺寸相同或各异的半导体元件,并且预置的固定结构有 效的防止半导体元件在受到外部冲击时产生滑移,可变性的连接件防止器件在工作时受到 冲击、震动、热胀冷缩等而产生变形甚至SiC半导体芯片受损,每个叠压板都具有温度和压 力检测装置用以防止因使用环境不当而造成的SiC半导体芯片寿命损耗。但是,该结构存在 4 CN 111554645 A 说 明 书 2/6 页 以下不足: 1、该结构并未考虑每个SiC半导体芯片的均衡散热; 2、该结构并未考虑各支路寄生电感分布的一致性。

技术实现要素:

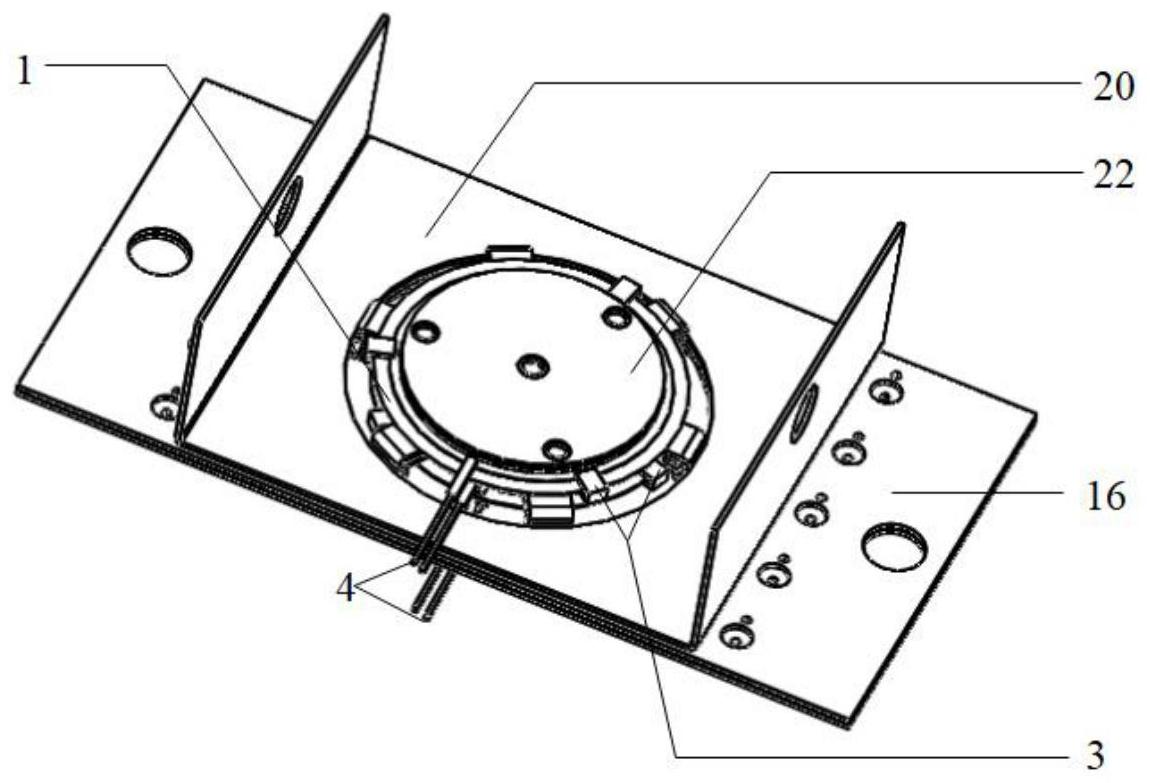

本发明的目的在于提供一种集成叠层母排的双面水冷SiC半桥模型封装结构。针 对目前封装技术寄生电感大问题,提出一种采用无引线键合的3D封装结构以及利用叠层母 排的方法来获得较小的寄生电感,并且,封装结构对称,可以使多个SiC半导体芯片并联结 构的各支路电感分布一致,以此获得良好的均流效果;采用双面水冷散热器可以获得优良 的散热效果,提高模块的可靠性。 为了达到上述目的,本发明提供一种集成叠层母排的双面水冷SiC半桥模块封装 结构,包括主体结构、外部连接结构和散热装置,所述主体结构包括一个上DBC、一个下DBC、 六个SiC半导体芯片和六个垫片,所述外部连接结构包括叠层母排和交流母排,叠层母排中 包括一个正极母排和一个负极母排,所述散热装置包括两个水冷散热器; 所述上DBC和下DBC结构完全相同,均包括一个DBC基板、两根驱动引针和三片铜 箔;所述DBC基板的横截面为圆形,从下至上依次为基板下铜层、基板陶瓷层和基板上铜层, 所述基板上铜层为图形化铜层,包括六块部分扇形铜、一条门极主干铜和三条门极分支铜; 六块部分扇形铜与基板陶瓷层保持同心并呈均匀分布状,一条门极主干铜以基板陶瓷层的 中心为起点延伸到基板陶瓷层边缘处,门极主干铜的尾部设有门极信号流入端子,三条门 极分支铜以基板陶瓷层的中心为起点,呈均匀分布状向三块部分扇形铜的短弧边中心方向 延伸,每个门极分支铜的尾部设有一个门极连接端子,门极连接端子与对应的部分扇形铜 之间留有间隙;所述驱动引针中的一根焊接在门极主干铜上、另一根焊接在基板下铜层上, 两根驱动引针在径向位置上对齐;所述铜箔的一端固接在基板下铜层上,另一端固接在与 门极分支铜对应的部分扇形铜上,三片铜箔的位置为均匀分布; 所述六个垫片和六个SiC半导体芯片均分为两组,第一组三个SiC半导体芯片的门 极分别与上DBC上的三个门极连接端子焊接在一起、源极分别与上DBC上门极分支铜相对应 的三块部分扇形铜焊接在一起、漏极分别与第一组三个垫片的一侧焊接在一起;第二组三 个SiC半导体芯片的门极分别与下DBC上的三个门极连接端子焊接在一起、源极分别与下 DBC上门极分支铜相对应的三块部分扇形铜焊接在一起、漏极分别与第二组三个垫片的一 侧焊接在一起; 所述正极母排和负极母排结构相同,均为一个矩形铜板,矩形铜板的中间位置留 有圆孔,圆孔的尺寸与DBC基板相适应,即保证DBC基板能够嵌装在圆孔中,在矩形铜板的两 端各有一个直流端子预留插口和一排去耦电容连接端子预留插口;三个引脚呈均匀分布安 装在正极母排的圆孔的孔边,三个引脚旋转60度后呈均匀分布安装在负极母排的圆孔的孔 边,在正极母排和负极母排的接触面上垫一层绝缘纸,将负极母排在上、正极母排在下压合 在一起构成叠层母排; 所述交流母排的形状为倒U型,包括一个矩形主板和两个矩形边板,主板和边板均 为铜板,在矩形主板的中间位置留有与叠层母排相同的圆孔,在两个矩形边板上各有一个 交流端子预留插口,六个引脚呈均匀分布安装在交流母排的圆孔的孔边; 5 CN 111554645 A 说 明 书 3/6 页 上DBC嵌装在交流母排的圆孔中,上DBC的部分扇形铜与交流母排的引脚相接,下 DBC嵌装在叠层母排的圆孔中,下DBC的部分扇形铜与叠层母排的引脚相接; 然后,将上DBC和下DBC的二条门极主干铜在径向方向上对齐后,将第一组三个垫 片的另一侧与下DBC上没有与门极分支铜相对应的三块部分扇形铜焊接在一起、第二组三 个垫片的另一侧与上DBC上没有与门极分支铜相对应的三块部分扇形铜焊接在一起,完成 了除散热装置之外的封装结构的装配; 所述散热装置包括两个结构相同的水冷散热器,每个水冷散热器的正面留有一个 入水口和三个出水口,入水口的位置为水冷散热器的中心,且三个出水口的位置与主体结 构中SiC半导体芯片的位置相对应,两个水冷散热器的反面分别通过导热油脂与上DBC、下 DBC的基板下铜层粘接在一起。 优选地,所述图形化铜层指的是在基板陶瓷层上采用敷接方法形成铜层,然后通 过刻蚀的方法形成不同的图形化布局。 优选地,所述SiC半导体芯片的源极和门极在SiC半导体芯片的同一面,漏极在SiC 半导体芯片的另外一面。 优选地,垫片的材料为与SiC半导体芯片具有相近热匹配系数的金属钼。 优选地,叠层母排的六个引脚与交流母排的六个引脚在径向位置上对齐。 优选地,两个水冷散热器的空腔中设有均匀分布的扰流柱。 由以上技术方案可知,与现有技术相比,本发明具有以下优势: 1、将叠层母排集成进封装结构中,不仅解决了功率端子大电感问题,而且叠层母 排和交流母排的对称性设计,可以尽量保证引脚到直流端子预留插口或者交流端子预留插 口的距离相差不大,从而使各支路的寄生参数尽量一致。 2、上DBC和下DBC设计成圆形结构以及对称布局,使得上DBC和下DBC的寄生电感分 布都趋于一致;由上DBC、下DBC、垫片、SiC半导体芯片构成的主体结构是3D结构,使得电流 能在垂直方向流动,由于垂直高度极小,为3mm左右,换流回路面积大大减小,因此可以有效 减小寄生电感。 3、两个水冷散热器分别与上DBC、下DBC的基板下铜层粘接在一起,实现双面水冷, 且三个出水口与SiC半导体芯片的位置相对应,使水流可以均衡的对每一个SiC半导体芯片 进行水冷,达到均衡散热的目的。 附图说明 图1为本发明封装结构的电路图; 图2为主体结构展开图; 图3为DBC基板结构示意图; 图4为DBC基板的图形化铜层结构示意图; 图5为图4中A处即芯片的门极连接端子放大图; 图6为焊接到上DBC或者下DBC的DBC基板上的SiC半导体芯片的分布图; 图7为安装垫片后的上DBC正面结构示意图; 图8为叠层母排结构示意图; 图9为去耦电容连接端子预留插口剖面图; 6 CN 111554645 A 说 明 书 4/6 页 图10为叠层母排展开图; 图11为叠层母排与下DBC连接剖面图; 图12为交流母排结构示意图; 图13为交流母排与上DBC连接示意图; 图14为上DBC与下DBC连接剖面图; 图15为上DBC与下DBC连接后正面结构示意图; 图16为集成散热装置后正面结构示意图; 图17为水冷散热器正面结构示意图; 图18为水冷散热器内部结构示意图; 图19为SiC半导体芯片正面结构放大图。 图20为上DBC和下DBC对应装配位置示意图 其中,1上DBC、2下DBC、3铜箔、4驱动引针针、5SiC半导体芯片、6垫片、7基板上铜 层、8基板陶瓷层、9基板下铜层、10部分扇形铜、11门极主干铜、12门极信号流入端子、13门 极连接端子、14正极母排、15负极母排、16叠层母排、17直流端子预留插口、18引脚、19去耦 电容连接端子预留插口、20交流母排、21交流端子预留插口、22水冷散热器、23源极、24入水 口、25出水口、26扰流柱、27门极分支铜、28门极。