技术摘要:

本发明提供了一种电流检测电路,包括并联低压差稳压器电路、电流复制读出电路和第一NMOS管,所述并联低压差稳压器电路的第一端与所述第一NMOS管的源极连接,所述并联低压差稳压器电路的第二端与所述电流复制读出电路连接,所述并联低压差稳压器电路的第三端连接被检测 全部

背景技术:

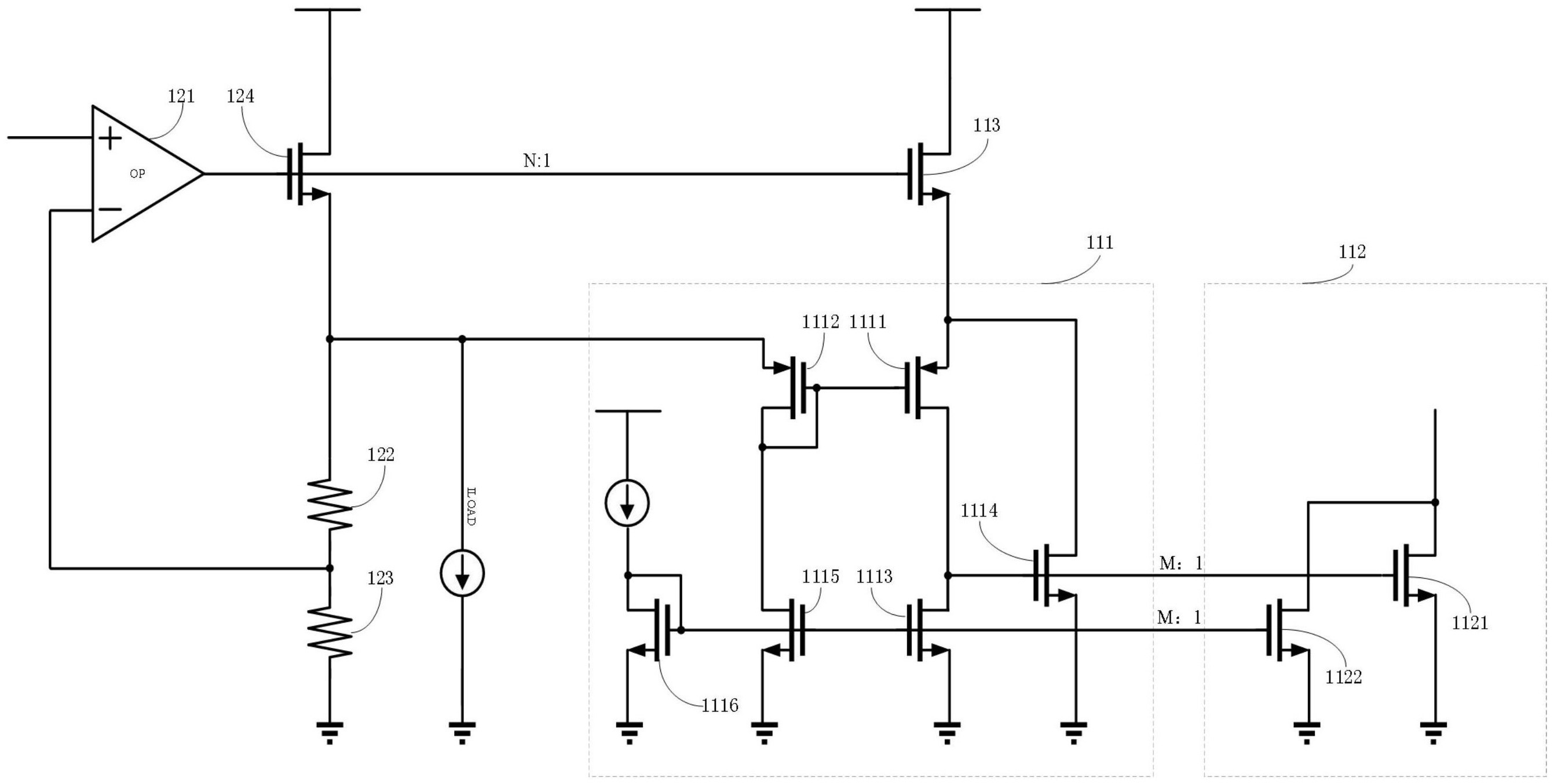

低压差稳压器功率表输出单元通常为PMOS管或NMOS管,图1为现有技术中的NMOS 管输出的低压差稳压器的电路图,包括误差放大器OP1、电阻R1、电阻R2以及NMOS管NM1, NMOS管NM1的漏极连接输入电压VIN,NMOS管NM1的源极连接电阻R2的一端,并输出电压 VOUT,电阻R2的另一端连接电阻R1的一端和误差放大器OP1的反相输入端,电阻R1的另一端 接地,误差放大器OP1的同相输入端输入参考偏置电压VREF,误差放大器OP1的输出端连接 NMOS管NM1的栅极,形成负反馈环路,以保证输出电压VOUT=VREF×(1 R1/R2)。 由上述可以看出,在NMOS管输出的低压差稳压器中,因负载轻重不同,输出电流变 化范围很大,导致输出电流无法被精确的检测,从而无法对负载起到过流保护和改善负载 调整率,无法维持负反馈环路在各种工作模式下的稳定性,也无法实现对接口的测试等。 因此,有必要提供一种新型的电流检测电路及低压差稳压器电路以解决现有技术 中存在的上述问题。

技术实现要素:

本发明的目的在于提供一种电流检测电路,实现对电流大小的检测。 为实现上述目的,本发明的所述电流检测电路,包括并联低压差稳压器电路、电流 复制读出电路和第一NMOS管,所述并联低压差稳压器电路的第一端与所述第一NMOS管的源 极连接,所述并联低压差稳压器电路的第二端与所述电流复制读出电路连接,所述并联低 压差稳压器电路的第三端连接被检测电压,所述第一NMOS管的栅极接控制电压,所述第一 NMOS管的漏极接输入电压。 本发明的有益效果在于:所述并联低压差稳压器电路的第一端与所述第一NMOS管 的源极连接,所述并联低压差稳压器电路的第二端与所述电流复制读出电路连接,所述并 联低压差稳压器电路的第三端用于连接被检测电压,所述第一NMOS管的栅极接控制电压, 所述第一NMOS管的漏极接输入电压,通过所述并联低压差稳压器电路检测电流,并通过所 述电流复制读出电路读出电流,从而实现了对被检测电压处电流大小的检测。 优选地,所述并联低压差稳压器包括形成负反馈环路的第一PMOS管、第二NMOS管 和第三NMOS管,所述第一PMOS管的源极和所述第三NMOS管的漏极均与所述第一NMOS管的源 极连接,所述第一PMOS管的漏极与所述第二NMOS管的漏极和所述第三NMOS管的栅极连接, 且所述第二NMOS管的源极和所述第三NMOS管的源极均接地。其有益效果在于:所述第一 PMOS管、所述第二NMOS管和所述第三NMOS管形成负反馈环路,可以保证流向所述第三NMOS 管的电流,经所述第三NMOS管流向地,且所述第一NMOS管源极处的电压不随所述第一NMOS 管的漏电流变化。 4 CN 111596118 A 说 明 书 2/4 页 进一步优选地,所述并联低压差稳压器还包括第二PMOS管和第四NMOS管,所述第 二PMOS管的源极连接所述被检测电压,所述第二PMOS管的栅极与所述第一PMOS管的栅极连 接,所述第二PMOS管的漏极与所述第四NMOS管的漏极连接,且所述第二PMOS管的栅极和漏 极短接,所述第四NMOS管的栅极与所述第二NMOS管的栅极连接,所述第四NMOS管的源极接 地。其有益效果在于:便于接入所述被检测电压。 进一步优选地,所述并联低压差稳压器还包括第五NMOS管,所述第五NMOS管的漏 极和栅极短接,且所述第五NMOS管的漏极接入偏置电流,所述第五NMOS管的栅极还与所述 第四NMOS管的栅极连接,所述第五NMOS管的源极接地。其有益效果在于:便于使所述第二 NMOS管和所述第四NMOS管作为电流源,以便于对被检测电压处电流大小的进行检测。 进一步优选地,所述第一PMOS管和所述第二PMOS管的尺寸比例与所述第四NMOS管 和所述第二NMOS管的尺寸比例相同。其有益效果在于:便于使所述第一NMOS管源极处的电 压等于所述第二PMOS管源极处的电压。 进一步优选地,所述电流复制读出电路包括第六NMOS管,所述第六NMOS管的栅极 与所述第三NMOS管的栅极连接,所述第六NMOS管的源极接地。其有益效果在于:便于通过所 述第六NMOS管成比例复制所述第三NMOS管的电流。 进一步优选地,所述电流复制读出电路还包括第七NMOS管,所述第七NMOS管的栅 极与所述第二NMOS管的栅极连接,所述第七NMOS管的漏极与所述第六NMOS管的漏极连接, 所述第七NMOS管的源极接地。其有益效果在于:便于通过所述第七NMOS管成比例复制所述 第二NMOS管的电流。 本发明还提供了一种应用电流检测电路的低压差稳压器电路,包括稳压器电路和 电流检测电路,电流检测电路包括并联低压差稳压器电路、电流复制读出电路和第一NMOS 管,所述并联低压差稳压器电路的第一端与所述第一NMOS管的源极连接,所述并联低压差 稳压器电路的第二端与所述电流复制读出电路连接,所述并联低压差稳压器电路的第三端 与所述稳压器电路连接,所述第一NMOS管的栅极与所述稳压器电路连接,所述第一NMOS管 的漏极接输入电压。 所述低压差稳压器电路的有益效果在于:所述并联低压差稳压器电路的第一端与 所述第一NMOS管的源极连接,所述并联低压差稳压器电路的第二端与所述电流复制读出电 路连接,所述并联低压差稳压器电路的第三端与所述稳压器电路连接,所述第一NMOS管的 栅极与所述稳压器电路连接,所述第一NMOS管的漏极接输入电压,以实现对所述稳压器电 路输出电流的检测。 进一步优选地,所述稳压器电路包括误差放大器、第一电阻、第二电阻和第八NMOS 管,所述误差放大器的输出端与所述第八NMOS管的栅极和所述第一NMOS管的栅极连接,所 述误差放大器的同相输入端接参考电压,所述误差放大器的反相输入端接所述第一电阻和 所述第二电阻的一端,所述第一电阻的另一端与所述第八NMOS管的源极和所述电流检测电 路的第三端连接,所述第二电阻的另一端接地。 进一步优选地,所述并联低压差稳压器包括第二PMOS管和第四NMOS管,所述第二 PMOS管的源极与所述第一NMOS管的源极连接,所述第二PMOS管的栅极与所述第一PMOS管的 栅极连接,所述第二PMOS管的漏极与所述第四NMOS管的漏极连接,且所述第二PMOS管的栅 极和漏极短接,所述第四NMOS管的栅极与所述第二NMOS管的栅极连接,所述第四NMOS管的 5 CN 111596118 A 说 明 书 3/4 页 源极接地。 附图说明 图1为现有技术中NMOS管输出的低压差稳压器的电路图; 图2为本发明的应用电流检测电路的低压差稳压器电路图。