技术摘要:

本发明提供一种阵列基板、显示面板以及阵列基板的制作方法。阵列基板包括衬底基板、设置于衬底基板上的薄膜晶体管、栅极线和源极线;栅极线和源极线相互绝缘,且用于驱动薄膜晶体管;薄膜晶体管包括:栅极、源极、栅极绝缘层、以及形成于栅极绝缘层上的像素电极、半导 全部

背景技术:

随着显示技术的发展,液晶显示器(Liquid Crystal Display,简称LCD)等平面显 示装置因具有高画质、省电、机身薄、无辐射等优点,而被广泛的应用于手机、电视、个人数 字助理、笔记本电脑等各种消费性电子产品中,成为显示装置中的主流。液晶显示面板一般 由相对设置的阵列基板、彩膜基板以及夹设在阵列基板和彩膜基板之间的液晶分子层组 成。 目前,阵列基板的制作方法中一般包括六次光刻工艺,该方法包括:第一步:在玻 璃基板上沉积金属层,进行第一次光刻,形成栅极;第二步,依次沉积栅极绝缘层和铟镓锌 氧化物IGZO半导体层,进行第二次光刻,以形成半导体图形;第三步,沉积保护层,并进行第 三次光刻,以形成保护图形;第四步,沉积源漏极金属层,并进行第四次光刻,以形成源极和 漏极;第五步,沉积钝化层和平坦化层,并进行第五次光刻工艺,以形成导电过孔;第六步, 沉积透明导电薄膜,并进行第六次光刻,以形成像素电极以及导电过孔和像素电极的连通 图形。 然而,上述现有技术的阵列基板,其制作过程需要经历六次光刻工艺制程,工艺复 杂,且制作成本高。

技术实现要素:

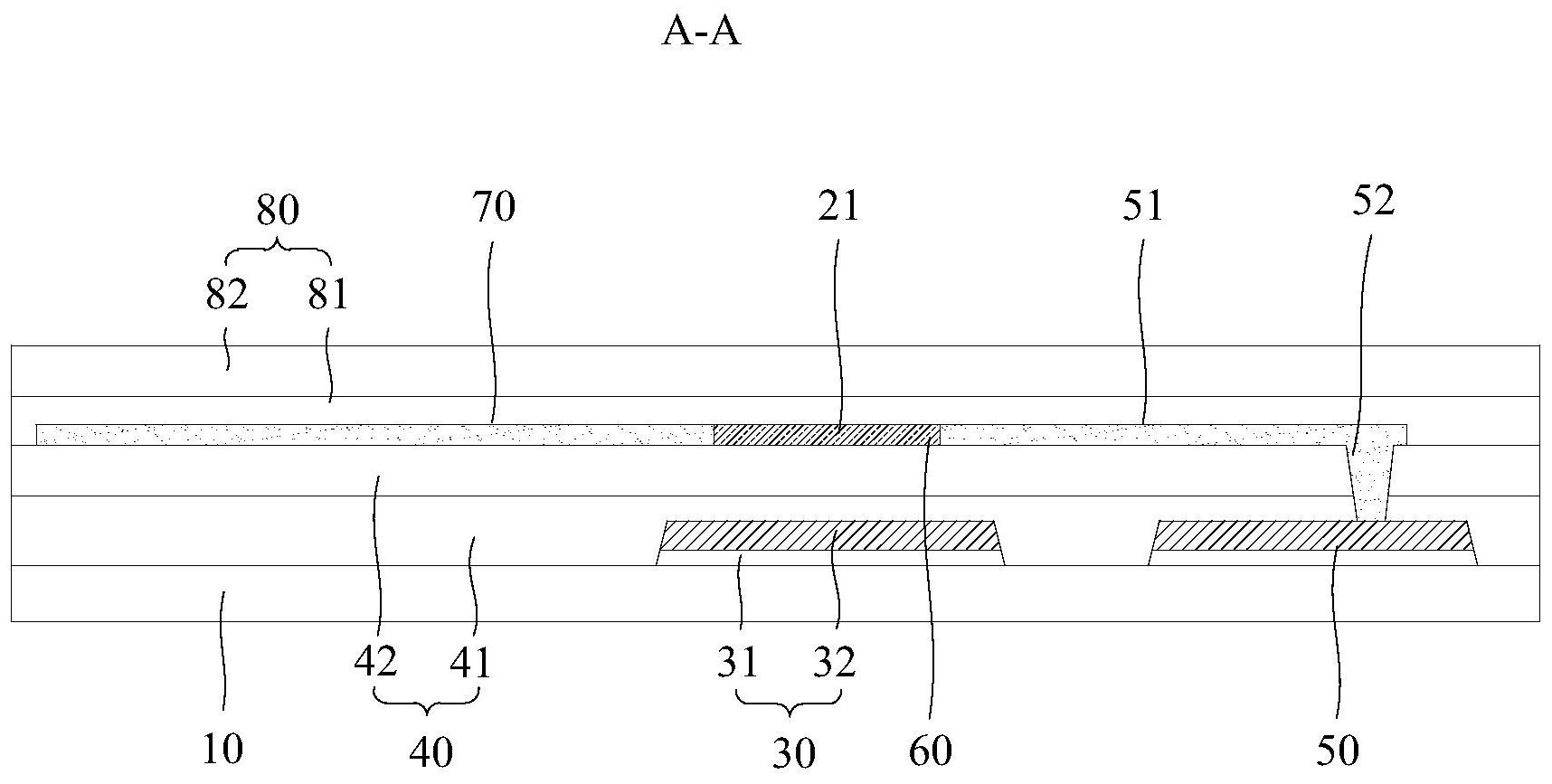

本发明提供一种阵列基板、显示面板以及阵列基板的制作方法,能够减少光刻工 艺次数,工艺简单且制造成本低。 本发明第一方面提供一种阵列基板,包括衬底基板、设置于衬底基板上的薄膜晶 体管、栅极线和源极线;栅极线和源极线相互绝缘,且用于驱动薄膜晶体管; 薄膜晶体管包括:栅极、源极、栅极绝缘层、以及形成于栅极绝缘层上的像素电极、 半导体图形和第一连接金属图形;其中,栅极和源极形成于衬底基板上,栅极绝缘层覆盖衬 底基板的形成有栅极和源极的表面,像素电极和第一连接金属图形相互间隔,且接续在半 导体图形两侧,以在半导体图形上形成沟道区域,半导体图形通过使导体材料半导体化而 成,第一连接金属图形与源极电连接。 本发明第二方面提供一种显示面板,包括上述的阵列基板。 本发明第三方面提供一种阵列基板的制作方法,包括在衬底基板上形成薄膜晶体 管、以及栅极线和源极线的步骤,在衬底基板上形成薄膜晶体管包括:在衬底基板上沉积栅 源金属层,并进行第一次光刻工艺,使栅源金属层形成栅极和源极;在形成有栅极和源极的 衬底基板上沉积栅极绝缘层,并进行第二次光刻工艺,以在栅极绝缘层上位于源极上方的 区域形成第一导电过孔;在栅极绝缘层上沉积透明导电层,并进行第三次光刻工艺,使透明 4 CN 111584520 A 说 明 书 2/12 页 导电层形成第一金属结构,第一金属结构对应半导体图形、像素电极、第一连接金属图案以 及第一导电过孔的区域;对第一金属结构上的部分区域进行半导体化,以形成半导体图形, 并形成位于半导体图形两侧且相互绝缘的像素电极和第一连接金属图形,并使第一连接金 属图形经由第一导电过孔和源极电连接。 本发明的阵列基板、显示面板以及阵列基板的制作方法。阵列基板包括衬底基板、 设置于衬底基板上的薄膜晶体管、栅极线和源极线;栅极线和源极线相互绝缘,且用于驱动 薄膜晶体管;薄膜晶体管包括:栅极、源极、栅极绝缘层、以及形成于栅极绝缘层上的像素电 极、半导体图形和第一连接金属图形;其中,栅极和源极形成于衬底基板上,栅极绝缘层覆 盖衬底基板的形成有栅极和源极的表面,像素电极和第一连接金属图形相互间隔,且接续 在半导体图形两侧,以在半导体图形上形成沟道区域,半导体图形通过使导体材料半导体 化而成,第一连接金属图形与源极电连接。通过源极和栅极同层,且形成在衬底基板上,因 此源极可以和栅极一起通过一次光刻工艺形成,将半导体图形、像素电极和第一连接金属 图形形成在栅极绝缘层上,像素电极和半导体图形接续,因此省略了传统意义上的漏极,并 且,与半导体图形接续的第一连接金属图形可与像素电极一起通过一次光刻工艺实现;这 与现有技术相比,至少省略了单独生成源极和漏极的光刻工艺,因此减少了光刻工艺的次 数,简化了阵列基板的形成过程,降低了制造成本。 附图说明 为了更清楚地说明本发明或现有技术的技术方案,下面将对实施例或现有技术描 述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些 实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些 附图获得其他的附图。 图1为本发明实施例一提供的阵列基板的俯视图; 图2为本发明实施例一提供的阵列基板的另一种结构的俯视图; 图3为本发明实施例一提供的阵列基板的A-A向剖视图; 图4为本发明实施例一提供的阵列基板的B-B向侧剖视图; 图5为本发明实施例三提供的阵列基板的制作方法中薄膜晶体管的制作方法的流 程示意图; 图6a为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第一状态时 的结构示意图; 图6b为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第一状态时 的另一角度的剖视图; 图7a为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第二状态时 的结构示意图; 图7b为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第二状态时 的另一角度的剖视图; 图8a为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第三状态时 的结构示意图; 图8b为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第四状态时 5 CN 111584520 A 说 明 书 3/12 页 的结构示意图; 图8c为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第五状态时 的结构示意图; 图8d为本发明实施例三提供的阵列基板的制作方法中另一种结构的阵列基板处 于第五状态时的结构示意图; 图8e为本发明实施例三提供的阵列基板的制作方法中另一种阵列基板的结构示 意图; 图9a为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第六状态时 的结构示意图; 图9b为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第六状态时 的另一角度的剖视图; 图10a为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第七状态时 的结构示意图; 图10b为本发明实施例三提供的阵列基板的制作方法中阵列基板处于第七状态时 的另一角度的剖视图。 附图标记: 100-阵列基板;10-衬底基板;20-薄膜晶体管;21-沟道区域;30-栅极;31-第一金 属层;32-第二金属层;40-栅极绝缘层;41-第一栅极绝缘层;42-第二栅极绝缘层;50-源极; 51-第一连接金属图形;52-第一导电过孔;53-第二导电过孔;60、62-半导体图形;61-第一 半导体图形;70-像素电极;71-像素电极主体;72-第二连接金属图形;73-透明导电层;74- 第一金属结构;80-钝化层;81-第一钝化层;82-第二钝化层;90-栅极线;91-源极线;92-架 桥部;93-贴合部;101-光刻胶图案;102-光刻胶部分保留区域;103-光刻胶完全保留区域。