技术摘要:

本发明涉及显示屏像素排列技术领域,特别涉及一种显示屏的像素排列结构,包括四个沿竖直方向依次排列的像素组,通过设置四个沿竖直方向依次排列的像素组,每个像素组均包括三个沿竖直方向依次排列且类型不同的元素组,每四个沿竖直方向依次排列的元素组构成一个像素单 全部

背景技术:

随着显示屏的高速发展,四边窄边框的显示屏已经成为主力发展趋势,高屏占比 给人以好的视觉效果;但是现有的显示屏中源极走线和驱动电路的使用数量均较多,这样 不仅会增大显示屏的边框,而且还增大了显示屏内部IC芯片的功耗。

技术实现要素:

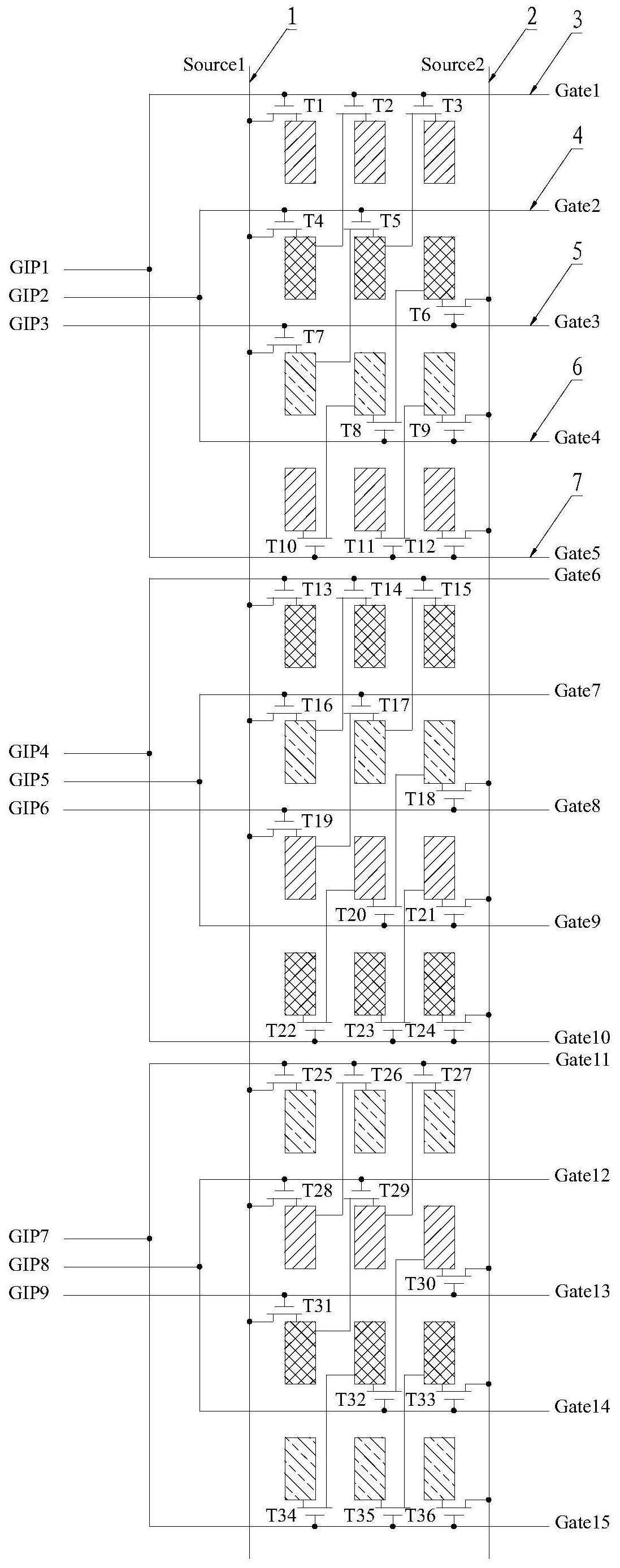

本发明所要解决的技术问题是:提供一种能够降低显示屏边框的显示屏的像素排 列结构。 为了解决上述技术问题,本发明采用的技术方案为: 一种显示屏的像素排列结构,包括四个沿竖直方向依次排列的像素组,每个所述 像素组均包括三个沿竖直方向依次排列且类型不同的元素组,每四个沿竖直方向依次排列 的所述元素组构成一个像素单元,每个所述像素单元均分别与外设的第一源极走线和第二 源极走线电连接,每个所述像素单元均通过五个相邻级的栅极走线分别与三个驱动电路电 连接。 本发明的有益效果在于: 通过设置四个沿竖直方向依次排列的像素组,每个像素组均包括三个沿竖直方向 依次排列且类型不同的元素组,每四个沿竖直方向依次排列的元素组构成一个像素单元, 这样使得显示屏源极走线的数量大大减少,与普通的显示屏相比,本方案设计的显示屏的 源极走线的数量只为普通的2/9,这样不仅能够缩小显示屏的下边框,而且还降低了显示屏 内部的IC芯片的功耗,减少了制作成本,提高了屏占比,同时显示效果也较佳。 附图说明 图1为根据本发明的一种显示屏的像素排列结构的结构示意图; 图2为根据本发明的一种显示屏的像素排列结构的结构示意图; 图3为根据本发明的一种显示屏的像素排列结构的第一驱动电路、第二驱动电路 和第三驱动电路的波形示意图; 标号说明: 1、第一源极走线;2、第二源极走线;3、第一级栅极走线;4、第二级栅极走线;5、第 三级栅极走线;6、第四级栅极走线;7、第五级栅极走线。