技术摘要:

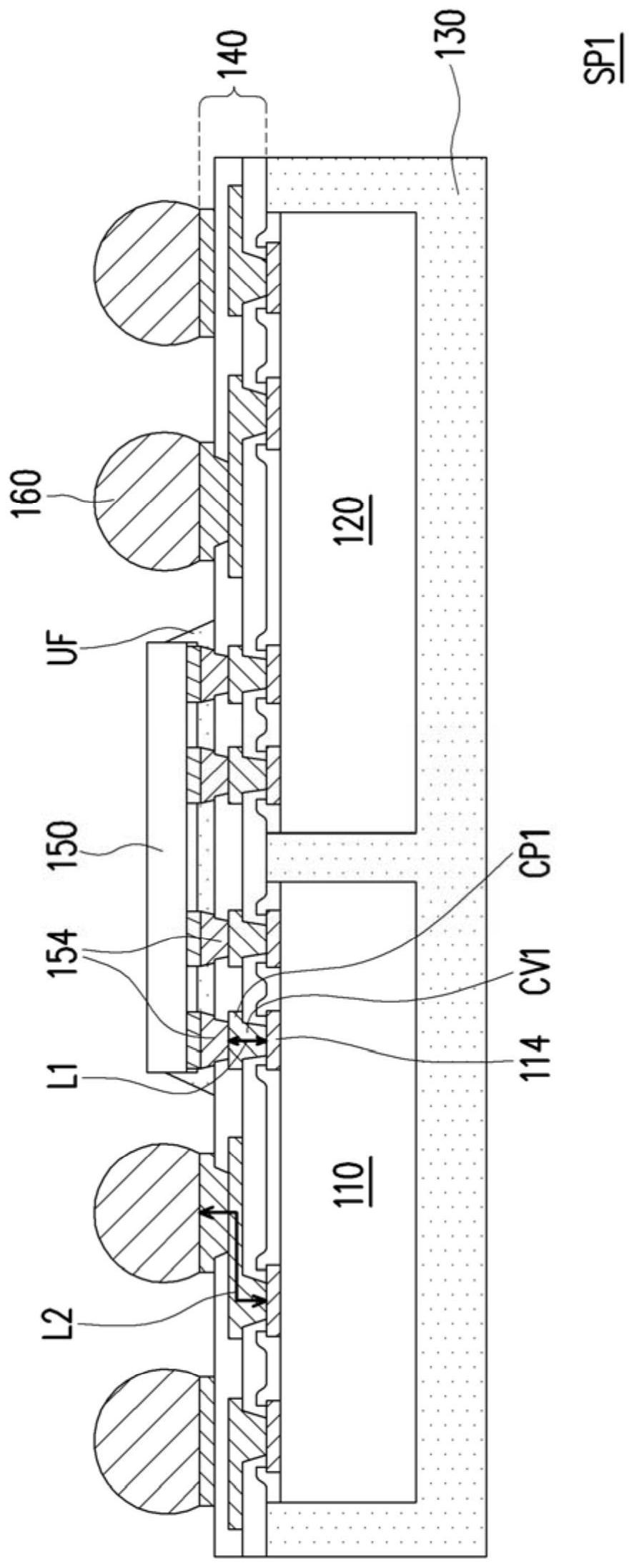

本发明提供一种半导体封装及其制造方法。半导体封装包括分别布置的第一和第二有源管芯、至少横向密封第一和第二有源管芯的绝缘包封体、设置在绝缘包封体及第一和第二有源管芯上的重布线层、以及设置在重布线层上并延伸超过第一和第二有源管芯之间的间隙的细间距管芯。 全部

背景技术:

近年来,电子设备对人类生活更为重要。为了使电子设备设计实现轻薄短小,半导 体封装技术不断发展,试图开发体积更小、重量更轻、整合度更高以及市场竞争更激烈的产 品。由于芯片封装技术受到集成电路发展的高度影响,故随着电子装置尺寸的变化,封装技 术的需求也变得越来越苛刻。因此,在保持工艺简单性的同时使半导体封装微型化已成为 该领域的研究人员的一大挑战。

技术实现要素:

本发明提供一种半导体封装及其制造方法,其可提供电气性能的改善以及更高的 可制造性。 本发明提供了一种半导体封装。半导体封装包括分别布置的第一有源管芯和第二 有源管芯、至少横向密封第一有源管芯和第二有源管芯的绝缘包封体、设置在绝缘包封体 及第一有源管芯和第二有源管芯上的重布线层、以及设置在重布线层上并延伸超过第一有 源管芯和第二有源管芯之间的间隙的细间距管芯。细间距管芯具有与第一有源管芯和第二 有源管芯不同的功能。细间距管芯的管芯连接件通过重布线层的第一导电路径连接到第一 有源管芯的导电特征,其中重布线层的第一导电路径的第一连接长度基本上等于细间距管 芯的管芯连接件和第一有源管芯的导电特征之间的最短距离。 在本发明的一实施例中,绝缘包封体的厚度大于第一有源管芯和第二有源管芯的 厚度。在本发明的一实施例中,第一有源管芯包括第一有源面和分布在第一有源面上的多 个导电特征,细间距管芯包括第二有源面和分布在第二有源面上的多个管芯连接件,第一 有源管芯的导电特征中的第一群组连接到细间距管芯的多个管芯连接件,并且第一有源管 芯的导电特征中的第二群组不连接到细间距管芯,以及分布在细间距管芯的第二有源面上 的管芯连接件的分布密度比分布在第一有源管芯的第一有源面上的导电特征中的第二群 组的分布密度更密集。在本发明的一实施例中,导电特征中的一群组设置在第一有源面的 周边并对应于重布线层的管芯安装区,其中细间距管芯设置在管芯安装区,以及群组中的 相邻的导电特征的间距基本上与对应于群组设置的细间距管芯的相邻的管芯连接件的间 距相匹配。 本发明提供一种半导体封装的制造方法。制造方法至少包括以下步骤。多个有源 管芯用绝缘包封体密装,其中相邻的有源管芯在空间上被绝缘包封体的一部分隔开。在有 源管芯和绝缘包封体上形成重布线层。细间距的管芯设置在重布线层上并在绝缘包封体的 一部分的上方,其中细间距管芯的管芯连接件接合到重布线层的导电路径。管芯连接件中 的任一者与有源管芯中的任一者之间的导电路径的连接长度基本上等于管芯连接件中的 4 CN 111599768 A 说 明 书 2/9 页 所述一者与有源管芯中的所述一者之间的最短距离。 在本发明的一实施例中,用绝缘包封体密封有源管芯包括将有源管芯分开地设置 在临时载体上,其中有源管芯的有源面朝向所述临时载体,以及在形成重布线层之前,将临 时载体从有源管芯上释出以暴露出有源管芯的有源面。在本发明的一实施例中,用绝缘包 封体密封有源管芯包括形成绝缘包封体以覆盖有源管芯中的每一者的侧壁和背面,其中背 面与重布线层相对并且侧壁连接到背面。在本发明的一实施例中,形成重布线层还包括在 图案化导电层上形成图案化介电层以部分地覆盖图案化导电层,其中在设置细间距管芯之 后,细间距管芯的管芯连接件的底部被图案化介电层横向覆盖,以与图案化导电层接触。在 本发明的一实施例中,半导体封装的制造方法还包括形成导电端子于重布线层上并在细间 距管芯旁,其中导电端子通过重布线层电性耦合到至少一个有源管芯。在本发明的一实施 例中,半导体封装的制造方法还包括在细间距管芯和重布线层之间形成底胶以至少横向覆 盖未被重布线层掩盖的细间距管芯的管芯连接件。在本发明的一实施例中,半导体封装的 制造方法还包括设置无源元件在重布线层上并在细间距管芯旁,其中无源元件通过重布线 层电性耦合到至少一个有源管芯。在本发明的一实施例中,当在重布线层上设置细间距管 芯时,对细间距管芯的管芯连接件执行回焊工艺。 基于上述,由于半导体封装包括以面对面配置设置的有源管芯和细间距管芯,以 缩短它们之间的互连距离,并可实现半导体封装的较低功耗和高频宽。细间距管芯可用于 提供高密度输入/输出(input/output,I/O)通信以互连相邻的有源管芯。通过使用上述制 造方法,可以将均质管芯(homogeneous die)和异质管芯(heterogeneous die)整合在单一 的扇出封装中。 附图说明 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详 细说明如下。 图1A至图1F是示出根据本发明的实施例的半导体封装的制造方法的示意性剖视 图; 图2是示出根据本发明的实施例的半导体封装的示意性剖视图。 [附图标号说明] 50、60:临时载板;51、61:离型层;110:第一有源管芯;110a、120a、150a:有源面; 110b、120b:背面;110c、120c:侧壁;112:半导体基板;114、124:接触垫;116:钝化层;120:第 二有源管芯;130:绝缘包封体;130b:底面;130t:顶面;140:重布线层;142:图案化介电层; 142a:第一图案化介电层;142b:第二图案化介电层;144:图案化导电层;144a:第一图案化 导电层;144b:第二图案化导电层;144’:图案化导电层;150:细间距管芯;152:半导体基板; 154:管芯连接件;154P:间距;154b:底部;160:导电端子;170:无源元件;BP:接合垫;CL:导 线;CP1、CP2、CP3:导电接垫;CV1、CV2、CV3:导通孔;DR:管芯安装区;GP1:第一群组;GP2:第 二群组;GP3:第三群组;GP4:第四群组;L1:第一连接长度;L2:第二连接长度;OP1:第一开 口;OP2:第二开口;OP3:第三开口;OP4:第四开口;SL:切割道;SP1、SP2:半导体封装;T1:厚 度;TR:端子安装区;UF:底胶。 5 CN 111599768 A 说 明 书 3/9 页