技术摘要:

本发明涉及一种半导体器件及其制造方法:第一导电类型衬底;第一导电类型外延层,位于所述第一导电类型衬底上方;沟槽,位于所述第一导电类型外延层内;第一导电类型扩散区,位于所述第一导电类型外延层内,且位于所述沟槽外围;第二导电类型外延层,位于所述沟槽内; 全部

背景技术:

功率器件防护芯片是一种用于保护敏感半导体器件,使其免遭瞬态电压浪涌破坏 而特别设计的固态半导体器件,它具有箝位系数小、体积小、响应快、漏电流小和可靠性高 等优点,因而在电压瞬变和浪涌防护上得到了广泛的应用。低电容功率器件防护芯片适用 于高频电路的保护器件,因为它可以减少寄生电容对电路的干扰,降低高频电路信号的衰 减。 静电放电(ESD)以及其他一些电压浪涌形式随机出现的瞬态电压,通常存在于各 种电子器件中。随着半导体器件日益趋向小型化、高密度和多功能,电子器件越来越容易受 到电压浪涌的影响,甚至导致致命的伤害。从静电放电到闪电等各种电压浪涌都能诱导瞬 态电流尖峰,功率器件防护芯片通常用来保护敏感电路不受到浪涌的冲击。基于不同的应 用,功率器件防护芯片可以通过改变浪涌放电通路和自身的箝位电压来起到电路保护作 用。 为了节省芯片面积,并且获得更高的抗浪涌能力。目前,常用的大电流功率器件防 护芯片的结构如图1所示,图中,1’表示P型硅衬底,2’表示N型扩散区域,3’表示多晶硅,该 功率器件防护芯片的寄生电容比较大、防护效果比较差。

技术实现要素:

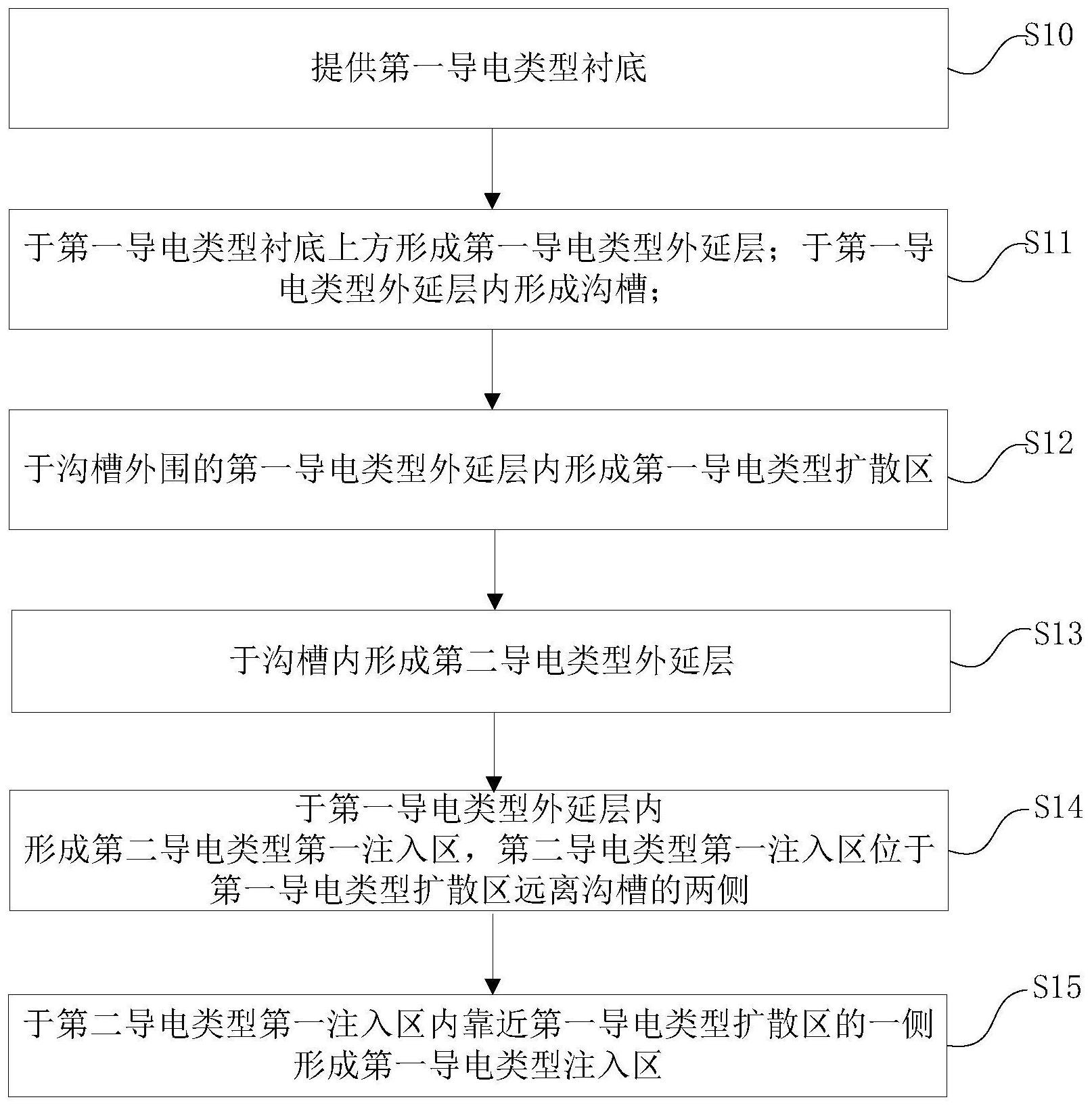

基于此,有必要针对现有的功率器件防护芯片寄生电容大、防护效果差的问题,提 供一种半导体器件及其制造方法,可以达到功率器件防护功能,并能降低器件寄生电容,漏 电小,可靠性高。 一种半导体器件,其特征是,所述的半导体器件包括: 第一导电类型衬底; 第一导电类型外延层,位于所述第一导电类型衬底上方; 沟槽,位于所述第一导电类型外延层内; 第一导电类型扩散区,位于所述第一导电类型外延层内,且位于所述沟槽外围; 第二导电类型外延层,位于所述沟槽内; 第二导电类型第一注入区,位于所述第一导电类型外延层内,且位于所述第一导 电类型扩散区远离所述沟槽的两侧; 第一导电类型注入区,位于对应的所述第二导电类型第一注入区内靠近所述第一 导电类型扩散区的一侧。 在其中一实施例中,还包括: 第二导电类型第二注入区,位于对应的所述第二导电类型第一注入区内远离所述 4 CN 111584480 A 说 明 书 2/8 页 第一导电类型扩散区的一侧。 在其中一实施例中,还包括: 第一金属层,与一所述第二导电类型第二注入区接触; 第二金属层,与所述第二导电类型外延层接触; 第三金属层,与另一所述第二导电类型第二注入区接触。 在其中一实施例中:两个所述第一导电类型注入区分别延伸至所述第一导电类型 扩散区。 在其中一实施例中:所述第一导电类型注入区的离子掺杂浓度大于所述第一导电 类型扩散区的离子掺杂浓度。 在其中一实施例中:所述第二导电类型第一注入区的深度大于所述第一导电类型 扩散区的深度; 所述第一导电类型注入区的深度小于所述第一导电类型扩散区的深度。 一种半导体器件的制造方法,其特征是,包括以下步骤: 提供第一导电类型衬底; 于所述第一导电类型衬底上方形成第一导电类型外延层; 于所述第一导电类型外延层内形成沟槽; 于所述沟槽外围的所述第一导电类型外延层内形成第一导电类型扩散区; 于所述沟槽内形成第二导电类型外延层; 于所述第一导电类型外延层内形成第二导电类型第一注入区,所述第二导电类型 第一注入区位于所述第一导电类型扩散区远离所述沟槽的两侧; 于所述第二导电类型第一注入区内靠近所述第一导电类型扩散区的一侧形成第 一导电类型注入区。 在其中一实施例中,还包括: 于所述第二导电类型第一注入区内远离所述第一导电类型扩散区的一侧形成第 二导电类型第二注入区。 在其中一实施例中:所述第一导电类型注入区自所述第二导电类型第一注入区内 延伸至所述第一导电类型扩散区内。 在其中一实施例中:所述第二导电类型第一注入区的深度大于所述第一导电类型 扩散区的深度; 所述第一导电类型注入区的深度小于所述第一导电类型扩散区的深度。 本发明提供的半导体器件及其制造方法,较现有技术具有以下优点: 通过在第一导电类型外延层内形成第二导电类型外延层,在该多层外延的结构基 础上形成两组横向二极管并联结构,降低了寄生电容; PN结采用第二导电类型外延层来形成,因此可以形成高浓度掺杂的PN结,其击穿 电压低,缺陷少,漏电少,器件可靠性高。 附图说明 图1为现有技术中的功率器件防护芯片的结构示意图; 图2为本发明的半导体器件的制造方法流程图; 5 CN 111584480 A 说 明 书 3/8 页 图3为本发明的半导体器件的制造方法的实施例中步骤S11所得半导体器件的结 构示意图; 图4为本发明的半导体器件的制造方法的实施例中步骤S12所得半导体器件的结 构示意图; 图5为本发明的半导体器件的制造方法的实施例中去除图4中的第一图形化掩膜 层以后所得的半导体器件的结构示意图; 图6为本发明的半导体器件的制造方法的实施例中步骤S13所得半导体器件的结 构示意图; 图7为本发明的半导体器件的制造方法的实施例中步骤S14所得半导体器件的结 构示意图; 图8为本发明的半导体器件的制造方法的实施例中步骤S15所得半导体器件的结 构示意图; 图9为本发明的半导体器件的制造方法的实施例中步骤S16所得半导体器件的结 构示意图; 图10为本发明的半导体器件的制造方法的实施例中步骤S172所得半导体器件的 结构示意图; 图11为本发明的半导体器件的制造方法的实施例中步骤S173所得半导体器件的 结构示意图; 图12为本发明的半导体器件的等效电路图。