技术摘要:

一种带输出箝位功能的运算放大器,能够应用于Buck变换器中,当Buck变换器工作在正常状态的时候,运算放大模块的输出小于预设的上限箝位电压且大于预设的下限箝位电压,上限箝位模块和下限箝位模块都工作在比较器状态,不会对运放的正常工作造成影响。当运算放大模块的 全部

背景技术:

在Buck型DC-DC变换器中,通常需要大电容进行补偿,保证系统的稳定性,当Buck 变换器从重载跳空载、或者输入电压突然比预设的输出电压低时,环路会进入0占空比或者 是100%占空比状态,导致运放输出会缓慢降低到0或者上升到电源电压。如果这时候负载 增大、或者输入电压恢复正常,运放的电流给补偿电容充放电,需要很长时间才能回到正常 电平,Buck变换器的输出电压将长时间处于异常状态。为了加快Buck变换器的响应速度可 以增大运放电流,增大运放电流虽然可以减小恢复时间,但是也会增大功耗。

技术实现要素:

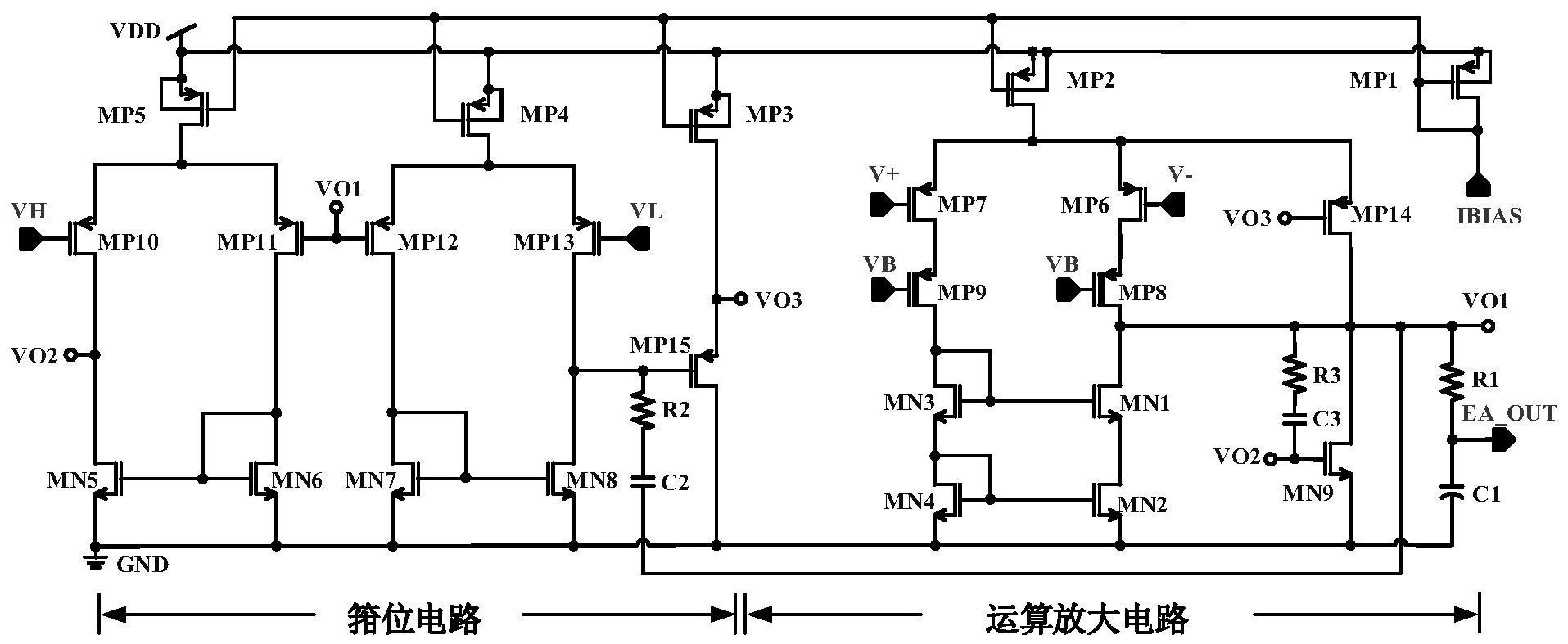

针对Buck变换器响应过程中恢复时间过大的不足之处,本发明提出一种带有输出 箝位功能的运算放大器,在运放中加入输出上限箝位和下限箝位功能,能够加快Buck变换 器的响应速度,节约功耗,解决了Buck变换器响应过程中恢复时间过大的问题。 本发明的技术方案为: 一种带输出箝位功能的运算放大器,包括运算放大模块、第一电阻、第一电容、偏 置模块、上限箝位模块和下限箝位模块, 所述偏置模块用于为所述运算放大模块、上限箝位模块和下限箝位模块提供偏 置,包括第一PMOS管,第一PMOS管的栅漏短接并连接偏置电流,其源极连接电源电压; 所述运算放大模块的正向输入端作为所述运算放大器的正向输入端,其负向输入 端作为所述运算放大器的负向输入端,其输出端依次通过第一电阻和第一电容后接地;第 一电阻和第一电容的连接点作为所述运算放大器的输出端; 所述上限箝位模块包括第五PMOS管、第十PMOS管、第十一PMOS管、第五NMOS管、第 六NMOS管、第九NMOS管、第三电阻和第三电容, 第五PMOS管的栅极连接第一PMOS管的栅极,其漏极连接第十PMOS管和第十一PMOS 管的源极,其源极连接电源电压; 第十PMOS管的栅极连接上限箝位电压,其漏极连接第五NMOS管的漏极和第九NMOS 管的栅极; 第十一PMOS管的栅极连接所述运算放大模块的输出端和第九NMOS管的漏极,其漏 极连接第六NMOS管的栅极和漏极以及第五NMOS管的栅极; 第五NMOS管、第六NMOS管和第九NMOS管的源极接地; 第三电阻一端连接所述运算放大模块的输出端,另一端通过第三电容后连接第九 NMOS管的栅极; 所述下限箝位模块包括第三PMOS管、第四PMOS管、第十二PMOS管、第十三PMOS管、 4 CN 111585516 A 说 明 书 2/5 页 第十四PMOS管、第十五PMOS管、第七NMOS管、第八NMOS管、第二电阻和第二电容, 第四PMOS管的栅极连接第三PMOS管的栅极和第一PMOS管的栅极,其漏极连接第十 二PMOS管和第十三PMOS管的源极,其源极连接第三PMOS管的源极并连接电源电压; 第十三PMOS管的栅极连接下限箝位电压,其漏极连接第八NMOS管的漏极和第十五 PMOS管的栅极; 第十二PMOS管的栅极连接所述运算放大模块的输出端和第十四PMOS管的漏极,其 漏极连接第七NMOS管的栅极和漏极以及第八NMOS管的栅极; 第七NMOS管和第八NMOS管的源极以及第十五PMOS管的漏极接地; 第十四PMOS管的栅极连接第三PMOS管的漏极和第十五PMOS管的源极,其源极连接 电源电压或偏置信号,所述偏置信号由与第一PMOS管构成电流镜的第十六PMOS管提供,第 十六PMOS管的栅极连接第一PMOS管的栅极,其源极连接电源电压,其漏极产生所述偏置信 号; 第二电阻一端连接第十五PMOS管的栅极,另一端通过第二电容后连接所述运算放 大模块的输出端。 具体的,所述运算放大模块包括第二PMOS管、第六PMOS管、第七PMOS管、第八PMOS 管、第九PMOS管、第一NMOS管、第二NMOS管、第三NMOS管和第四NMOS管, 第二PMOS管的栅极连接第一PMOS管的栅极,其源极连接电源电压,其漏极连接第 六PMOS管和第七PMOS管的源极; 第七PMOS管的栅极作为所述运算放大模块的正向输入端,其漏极连接第九PMOS管 的源极; 第六PMOS管的栅极作为所述运算放大模块的负向输入端,其漏极连接第八PMOS管 的源极; 第八PMOS管的栅极连接第九PMOS管的栅极和偏置电压,其漏极连接第一NMOS管的 漏极并作为所述运算放大模块的输出端; 第三NMOS管的栅漏短接并连接第九PMOS管的漏极和第一NMOS管的栅极,其源极连 接第四NMOS管的栅极和漏极以及第二NMOS管的栅极; 第二NMOS管的漏极连接第一NMOS管的源极,其源极连接第四NMOS管的源极并接 地。 具体的,所述第十六PMOS管为所述运算放大模块中的第二PMOS管。 具体的,所述第八PMOS管和第九PMOS管为低阈值PMOS管。 本发明的有益效果为:本发明在运放中加入输出上限箝位和下限箝位功能,能够 适用于Buck变换器;在Buck变换器正常工作时,上限箝位电路和下限箝位电路工作在比较 器状态,不对运放的正常工作造成影响;当运算放大模块的输出VO1大于上限箝位电压VH的 时候,限箝位电路会对运放的输出进行箝位,当运算放大模块的输出VO1小于下限箝位电压 VL的时候下限箝位电路会对运放的输出VO1进行箝位,因此本发明提出的运算放大器应用 于Buck变换器时,能够加快Buck变换器的响应速度,节约功耗。 附图说明 图1为本发明提出的一种带输出箝位功能的运算放大器在实施例中的具体电路 5 CN 111585516 A 说 明 书 3/5 页 图。