技术摘要:

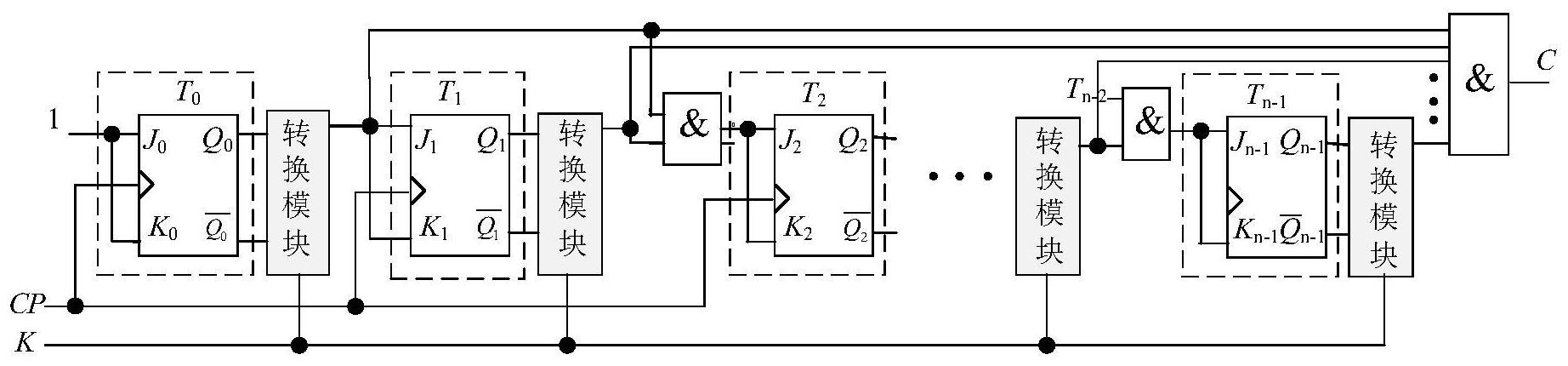

本发明提供一种同步n位二进制可逆计数器及其设计方法,同步n位二进制可逆计数器包括第一至第n共n个T触发器、第一至第n共n个转换模块和第一至第n共n个与门电路,其中,第一T触发器的输入端接逻辑1,第二至第nT触发器的输入端分别与第一至第n‑1与门电路的输出端一一对应 全部

背景技术:

“计数”是指对时钟脉冲个数的累计,实现计数功能的数字逻辑电路称为计数器 (Counter)。计数器是最常用的时序逻辑电路,在计算机中得到广泛应用,它不仅能用于对 时钟脉冲的计数,还可以用于定时、分频及进行数字运算等。计数脉冲可以是周期性脉冲, 也可以是非周期性脉冲,通常加在计数器的时钟输入端,作为计数器的时钟脉冲。 计数器的种类按计数器中触发器翻转的时序异同分类,可分为同步计数器和异步 计数器。按计数器在计数过程中数码的变化规律分类,可分为加法计数器、减法计数器和可 逆计数器。其中,加法计数器可随计数脉冲的不断输入递增计数;减法计数器可随计数脉冲 的不断输入递减计数;可逆计数器可在外加控制信号的作用下,随计数脉冲的不断输入既 可以加法计数也可以进行减法计数,也称为加/减计数器。按计数器的计数容量(计数长度) 来分,可分为n位二进制计数器,即2n进制计数器和N进制计数器,即任意进制计数器。其中, n位二进制计数器的电路有2n(如2、4、8、16、32…)个状态;N进制计数器的电路有N个状态(N ≠2n),如五进制计数器、七进制计数器、十进制计数器。 一般集成电路计数器都是n位二进制计数器结构,通过清零法或反馈预置法就可 以得到N进制计数器,应用广泛。 目前常用的一些n位二进制计数器的设计方式,在n较小时是可行的。然而当n较大 时,设计的计数器电路比较复杂,过程麻烦,而且对于不同的n值都要重复设计,工作量很 大。

技术实现要素:

本发明为解决上述技术问题,提供了一种同步n位二进制可逆计数器及其设计方 法,设计过程和所设计出的电路结构均比较简单,且适用于任意位二进制可逆计数器,大大 减小了电路设计的工作量。 本发明采用的技术方案如下: 一种同步n位二进制可逆计数器,包括第一至第n共n个T触发器、第一至第n共n个 转换模块和第一至第n共n个与门电路,其中,第一T触发器的输入端接逻辑1,第二至第nT触 发器的输入端分别与第一至第n-1与门电路的输出端一一对应连接,第一至第nT触发器的 第一输出端分别与第一至第n转换模块的第一输入端一一对应连接,第一至第nT触发器的 第二输出端分别与第一至第n转换模块的第二输入端一一对应连接,第i与门电路具有i个 输入端,i个输入端分别与第一至第i转换模块的输出端一一对应连接,第一至第nT触发器 的时钟输入端均接时钟信号,第一至第n转换模块的控制端均接控制信号,第n与门电路的 输出端作为所述同步n位二进制可逆计数器的进位信号输出端,其中,n为正整数且n>3,1 3 CN 111600599 A 说 明 书 2/7 页 ≤i≤n。 所述转换模块为二选一数据选择器。 所述转换模块包括非门电路和第一至第三共3个与非门电路,其中,所述非门电路 的输入端作为所述转换模块的控制端,第一与非门电路的一个输入端作为所述转换模块的 第一输入端,第一与非门电路的另一个输入端与所述非门电路的输入端相连,第二与非门 电路的一个输入端作为所述转换模块的第二输入端,第二与非门电路的另一个输入端与所 述非门电路的输出端相连,第三与非门电路的一个输入端与第一与非门电路的输出端相 连,第三与非门电路的另一个输入端与第二与非门电路的输出端相连,第三与非门电路的 输出端作为所述转换模块的输出端。 第一至第n转换模块的控制端输入不同的控制信号以分别实现加法计数和减法计 数。 一种同步n位二进制可逆计数器的设计方法,包括以下步骤:设计同步3位二进制 加法计数器;根据所述同步3位二进制加法计数器设计同步n位二进制加法计数器;根据所 述同步3位二进制加法计数器设计同步3位二进制减法计数器;根据所述同步3位二进制减 法计数器设计同步n位二进制减法计数器;根据所述同步n位二进制加法计数器和所述同步 n位二进制减法计数器设计所述同步n位二进制可逆计数器。 本发明的有益效果: 本发明通过依次设计同步3位二进制加法计数器、同步n位二进制加法计数器、同 步3位二进制减法计数器、同步n位二进制减法计数器,最终得到同步n位二进制可逆计数 器,设计过程和所设计出的电路结构均比较简单,且适用于任意位二进制可逆计数器,大大 减小了电路设计的工作量。 附图说明 图1为本发明一个实施例的同步n位二进制可逆计数器的电路图; 图2为本发明一个实施例的转换模块的结构框图; 图3为本发明一个实施例的转换模块的电路图; 图4为本发明实施例的同步n位二进制可逆计数器的设计方法的流程图; 图5为本发明一个实施例的同步3位二进制加法计数器的电路图; 图6为本发明一个实施例的同步3位二进制加法计数器的状态转换图; 图7为本发明一个实施例的同步n位二进制加法计数器的电路图; 图8为本发明一个实施例的同步3位二进制减法计数器的状态转换图; 图9为本发明一个实施例的同步3位二进制减法计数器的电路图; 图10为本发明一个实施例的同步n位二进制减法计数器的电路图; 图11为本发明一个实施例的同步3位二进制可逆计数器的电路图。