技术摘要:

本发明公开了一种双端口静态随机存取内存,包括第一MOS第一端作为差动位线A端口一,第一MOS第二端连接第二MOS第二端、第三MOS第三端、第五MOS第二端、第六MOS第二端、第七MOS第三端,第一MOS第三端连接第四MOS第三端作为内存字线A;第二MOS第一端连接电源电压,第二MOS 全部

背景技术:

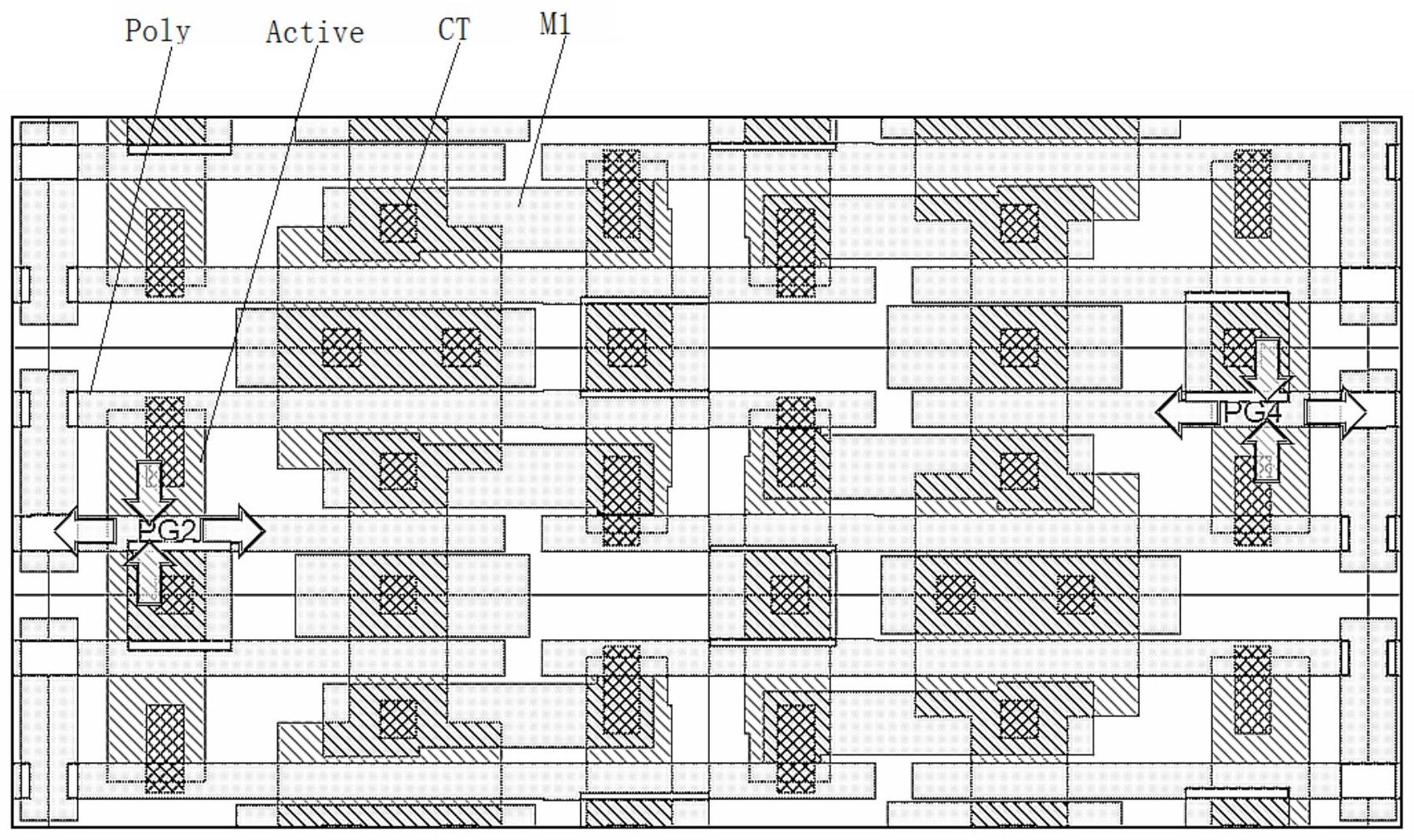

静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器 的一种。SRAM是比动态随机存取存储器(DRAM)更为昂贵,但更为快速、非常低功耗(特别是 在空闲状态)。因此SRAM首选用于带宽要求高,或者功耗要求低,或者二者兼而有之。 在半导体的数字逻辑芯片代工部份,经常使用静态随机存取内存作为储存位的工 具,其中八个晶体管(8T:8transistor)组成的双端口静态随机存取内存(Dual port SRAM) 具有双端口皆可以有读取与写入的功能。如图1结合图2所示,一种现有晶体管组成双端口 静态随机存取内存电路,包括8个晶体管PD1、PD2,PU1、PU2、PG1、PG2、PG3和PG4。一条地址线 搭配两条差动位线称之为一个端口,双端口为的第一个端口为字线A_WL控制PG1与PG2分别 连接差动位线A_BL和差动位线A_BLB,双端口第二个端口为字线B_WL控制PG3与PG4分别连 接差动位线B_BL和差动位线B_BLB。 传统方式,同一个端口的晶体管在做读取时的路径是不一致的,A Port的PG1与 PG2不一致,B port的PG3与PG4不一致。一般来说八个晶体管组成双端口静态随机存取内存 的端口是一致的,所以组件PG1,PG2,PG3,PG4的关键尺寸(width/length)都是一样的,但是 由于传统的布局的关系造成不一致,导致读取时的路径不同。 参考图3、图4所示,A_BL(PG1)读取电流Iread 1与B_BL(PG3)读取电流Iread 3路 径示意图。Iread 1(PG1)路径,从A_BL经过PG1,PD1接至Vss,Iread 3(PG3)路径,从B_BL经 过PG2,PD2接至Vss。 参考图5、图6所示,A_BLB(PG2)读取电流Iread 2与B_BLB(PG4)读取电流Iread 4 路径示意图。Iread 2(PG2)路径,从A_BLB经过PG2,Poly与Metal线路,PD1接至Vss,Iread 4 (PG4)路径,从B_BLB经过PG4,Poly与Metal线路,PD2接至Vss。图5和图6中路径比图3、图4多 一段多晶硅Poly与金属层Metal线路,代表的是此段线路多了一些阻抗,因此Iread 2与 Iread 4读取电流会比Iread 1与Iread 3低一些,所读取操作的速度会慢一些。传统的双端 口静态随机存取内存(8T Dual Port SRAM)由于电流路径不同所造成读取电流不一致,导 致不同的端口做读取,速度不对称,不同的端口速度会有快有慢的差异。

技术实现要素:

在