技术摘要:

本发明属于芯片配置网络技术领域,特别涉及一种灵活支持混合总线协议的芯片配置网络系统,包括配置网络主从接口、协议解析与地址映射模块和核心互连网络;在配置网络主从接口处分别增加协议解析与地址映射模块;所述协议解析与地址映射模块用于实现总线读写请求/读写响 全部

背景技术:

芯片配置网络主要用于支撑芯片中各主配接口(如I2C、JTAG、PCIE等)对芯片内部 的相关寄存器或RAM空间的配置和管理,为芯片功能和性能的实现提供基础性保障。随着芯 片设计规模的不断增大,芯片内部配置网络的设计规模和设计复杂度也随之增大。一方面, 配置网络支持的主(Master)从(Slave)接口规模越来越大,大规模系统芯片内部配置网络 的主从接口数已超过100个;另一方面,为了缩短产品上市时间,芯片内部通常会集成多种 多样的商用IP(知识产权核),这些商用IP在芯片中可能位于配置网络的主口(Master)位 置,也位于配置网络的从口(Slave)位置,甚至既有从接口也有主接口与配置网络相连。此 外,不同的商用IP可能采用不同的总线协议(如AXI、AHB、APB等),使得芯片内部可能同时存 在多种不同协议类型的总线配置需求,进而导致设计复杂度的急剧增大。 以某SRIO交换芯片的配置网络设计为例,如图1所示。根据总体设计需求,SRIO交 换芯片内部配置网络的主从接口规模达到近百个,且同时存在着AXI总线、AHB总线、SRIO维 护包(总线读写请求)、Localbus总线等多种不同的总线协议类型。为了满足芯片的配置需 求,传统的设计思路是芯片内部集成多个相应协议的总线互连矩阵Matrix(用于多主多从 的通信场景)以及不同协议的桥接(Bridge)模块,用于实现同一总线协议主从接口之间的 数据转发以及不同总线协议之间的协议转换。如图1所示,AXI_Matrix用于实现多个AXI协 议主从接口之间的通信,AHB_Matrix用于实现多个AHB协议主从接口之间的通信,AXI_To_ AHB_Bridge用于实现AXI协议与AHB协议之间的转换,AHB_To_Localbus_Bridge用于实现 AHB协议与Localbus总线之间的转换,SRIO MPM(Maintenance Processing Module)用于实 现SRIO维护包配置请求与AXI总线协议之间的转换等。鉴于总线协议处理的复杂性和兼容 性,配置网络中大量总线互连Matrix和Bridge模块的集成将给其设计和验证均带来极大的 挑战。 在主从接口众多、多种总线协议混合的应用通信需求下,现有配置网络设计中所 广泛采用的总线互连Matrix与总线Bridge的设计方法通常存在着以下缺点: (1)设计难度大、技术门槛高。总线互连Matrix与总线Bridge的设计通常是针对读 写地址信号、数据信号以及读写响应信号进行信号级的处理,需要设计人员不仅熟悉总线 协议各信号之间的依赖关系和处理流程,还需要掌握相应协议互连Matrix的设计方法以及 不同总线协议之间的转换实现,设计难度较大,具有较高的技术门槛。 (2)不同总线协议转换的兼容性和一致性难以保证。总线互连Matrix与总线 Bridge的设计需要严格遵循相应的总线协议,且不同总线协议转换的兼容性和一致性难以 保证,设计不当极易造成网络的死锁现象,甚至影响整个芯片的功能和性能。 (3)可扩展性和重用性较差。总线互连Matrix与总线Bridge的设计一旦确定,网络 4 CN 111555901 A 说 明 书 2/6 页 规模的少量更改或总线接口协议的变化均将引入较大的设计修改与验证工作量,难以灵活 地扩展至不同的通信规模和应用通信场景,可扩展性和重用性较差。

技术实现要素:

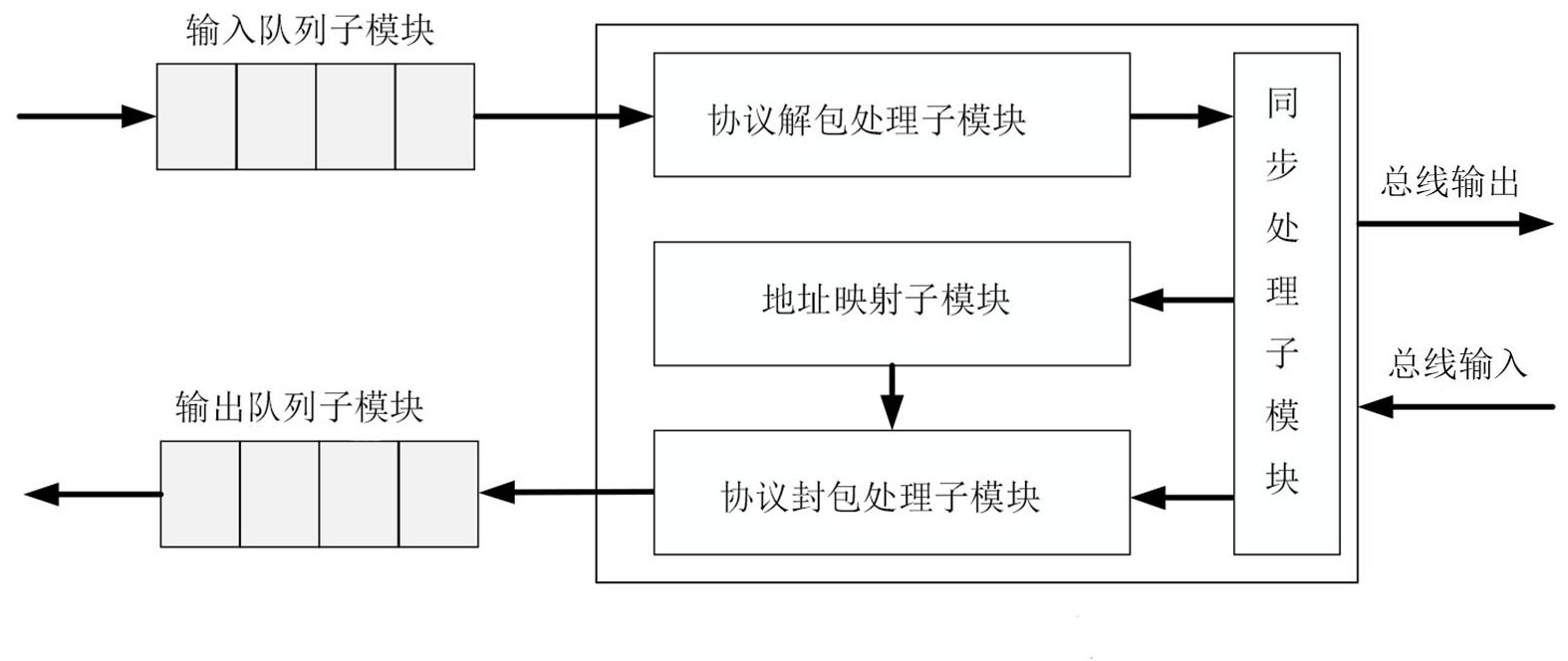

为了解决现有技术中存在的问题,本发明提供了一种灵活支持混合总线协议的芯 片配置网络系统,不仅可灵活地支持常用的AMBA总线(如AXI/AHB/APB等)、处理器二级总线 (如Localbus等)、SRIO维护包配置总线、用户自定义总线等多种总线协议的网络互连和协 议桥接,还可大大降低芯片配置网络的设计复杂度和技术门槛,并兼具良好地可扩展性和 重用性。 为解决上述技术问题,本发明采用以下的技术方案: 本发明的一种灵活支持混合总线协议的芯片配置网络系统,包括:配置网络主从 接口、协议解析与地址映射模块和核心互连网络;在配置网络主从接口处分别增加协议解 析与地址映射模块,协议解析与地址映射模块与核心互连网络连接;所述协议解析与地址 映射模块用于实现总线读写请求/读写响应地址与网络ID之间的转换,以及将不同总线协 议的读写请求或读写响应按照统一的格式转化为数据包的形式并注入核心互连网络,或将 从核心互连网络接收的数据包根据不同的总线协议转换为相应的总线信号时序,数据包在 核心互连网络中传输时具有协议无关性。 进一步地,所述协议解析与地址映射模块包括同步处理子模块、协议封包处理子 模块、地址映射子模块、协议解包处理子模块、输入队列子模块和输出队列子模块; 所述同步处理子模块,用于完成信号在总线时钟与网络时钟之间的跨时钟域处 理; 所述协议封包处理子模块,用于根据总线协议将总线读写请求/读写响应封装成 数据包的形式; 所述地址映射子模块,用于总线读写请求/读写响应地址与网络DEST_ID之间的映 射,该DEST_ID封装至数据包中,用于在核心互连网络中选路; 所述协议解包处理子模块,用于接收网络中传送过来的数据包,并根据不同的总 线协议转换成相应的总线信号时序; 所述输入队列子模块,用于接收网络传送过来的数据包,生成相应的反压信号输 送给网络,并在总线读写请求/读写响应信号的控制下上传数据包至协议解包处理子模块 进行后续解包处理; 所述输出队列子模块,用于接收总线读写请求/读写响应经协议封包处理子模块 后产生的数据包,生成相应的反压信号给总线接口,并在网络空闲时将输出队列子模块中 的数据包注入网络。 进一步地,不同总线协议的读写请求或读写响应在网络中具有统一的数据包格 式,其数据包格式如下: Tail Body … Body Header 该数据包由头微片(Header Flit)、体微片(Body Flit)和尾微片(Tail Flit)三 种数据结构组成,其中,头微片携带路由信息和相关总线控制信息,体微片和尾微片携带读 写数据信息与数据包结束指示,三种微片的数据宽度均与网络接口的数据位宽相匹配。 5 CN 111555901 A 说 明 书 3/6 页 进一步地,头微片的格式如下: Tag Resp Data Des_ID Src_ID Wr_addr Pkt_type Pro_type Flit_type 体微片或者尾微片的格式如下: Data Data Data Data Flit_type Flit_type表示微片的类型,Pro_type表示协议的类型,Pkt_type表示数据包的类 型,Wr_addr表示总线读写地址,Src_ID表示报文的源ID地址,Des_ID表示报文的目的ID地 址,Data表示总线读写数据,Resp表示读写响应,Tag表示保存总线协议中需要关注的其他 重要控制信息。 进一步地,芯片配置网络中的核心互连网络采用Crossbar Switch方式或者基于 NOC片上互连方式,当芯片配置网络主从节点较少时,采用Crossbar Switch结构,当芯片配 置网络主从节点较多时,采用基于NOC片上互连结构。 与现有的总线互连Matrix与总线Bridge设计方法相比,本发明具有以下优点: 1、降低配置网络设计的复杂度:本发明的灵活支持混合总线协议的芯片配置网络 系统解决了总线互连Matrix与总线Bridge设计复杂度的问题,通过在协议解析与地址映射 模块(PRAM)接口处对不同总线协议的读写请求或读写响应进行封包和解包处理,可以灵活 支持相同协议之间的网络互连以及不同协议之间的桥接处理,并避免网络协议处理中各种 复杂信号依赖性保障及其协议处理流程,协议处理的兼容性与一致性也容易得到保证。 2、规避网络死锁、活锁与饿死现象的发生:不同的总线协议以统一的数据包格式 在网络中进行传输,在网络中采用成熟的免死锁路由算法或基于公平的仲裁策略,即可有 效规避网络死锁、活锁以及饿死现象的发生。 3、具有较好的可重用性以及扩展性:通过增加核心互连网络的通信规模以及PRAM 接口的协议适用性,可灵活适用于不同网络规模以及不同协议类型的通信场景。此外,经过 充分验证的PRAM模块可直接运用于不同的应用场景,具有较好的可重用性。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明 的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据 这些附图获得其他的附图。 图1是现有技术某SRIO交换芯片配置网络结构示意图; 图2是本发明实施例的灵活支持混合总线协议的芯片配置网络系统的结构示意 图; 图3是本发明实施例的协议解析与地址映射模块的结构示意图; 图4是本发明实施例的协议封包处理子模块和协议解包处理子模块的工作流程 图,其中(a)是协议封包处理子模块的工作流程图,(b)是协议解包处理子模块的工作流程 图; 图5是基于2D-MESH NOC的芯片配置网络结构示意图。 6 CN 111555901 A 说 明 书 4/6 页