技术摘要:

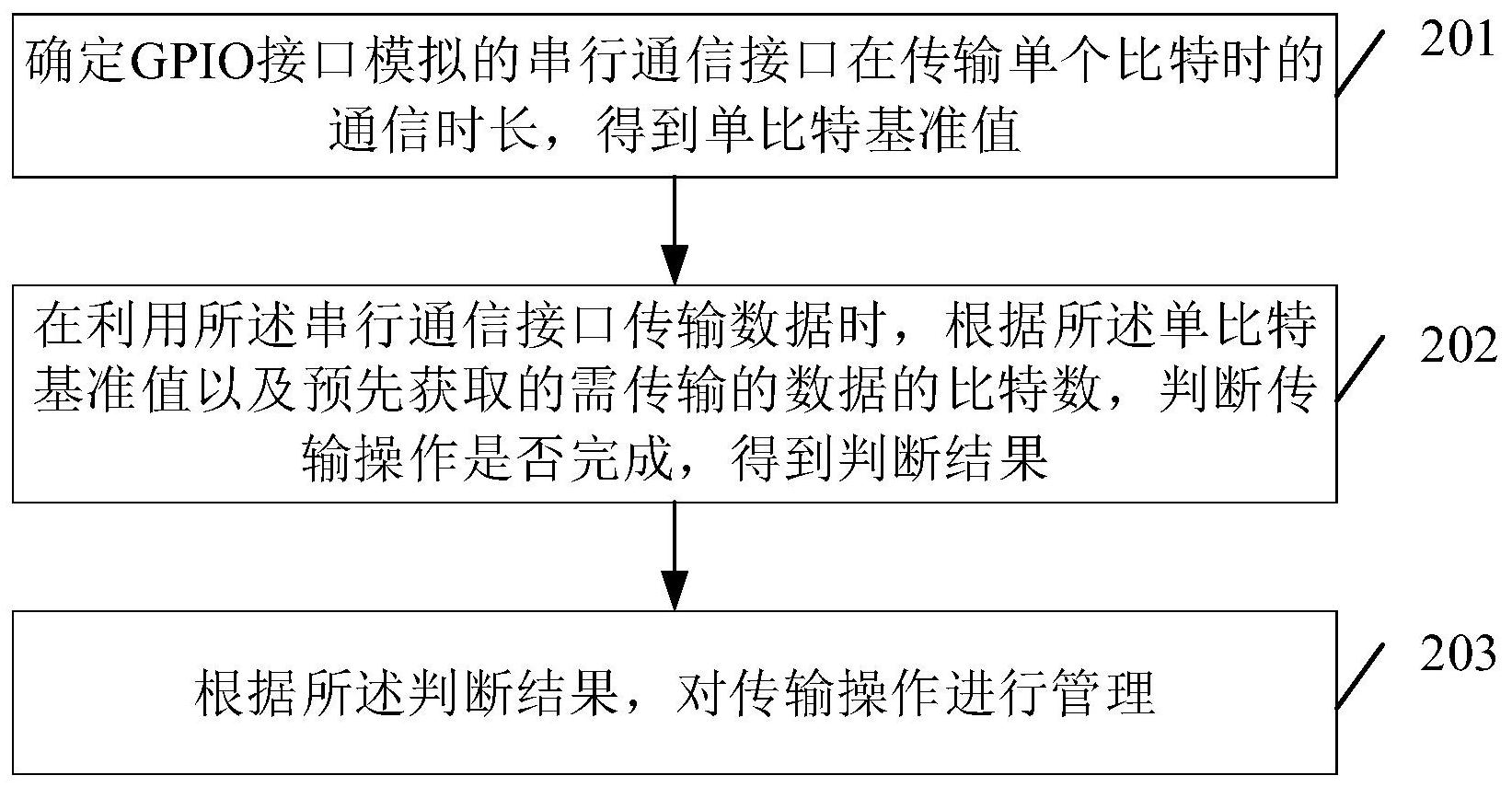

本申请实施例公开了一种嵌入式芯片中传输控制方法和装置。所述方法包括:确定通用型输入输出GPIO接口模拟的串行通信接口在传输单个比特时的通信时长,得到单比特基准值;在利用所述串行通信接口传输数据时,根据所述单比特基准值以及预先获取的需传输的数据的比特数, 全部

背景技术:

随着当前嵌入式芯片技术的发展,应用设计对嵌入式芯片的要求不断提高,产品 开发需要更多的串行通信接口与外围设备连接通信。芯片厂商由于成本以及芯片应用不会 设计太多的串行通信接口,需要产品应用开发软件方式GPIO(General-purpose input/ output,通用型输入输出)模拟串行通信接口。 图1为相关技术中利用软件模拟串行通信接口的接收方法的流程图。如图1所示, 所述方法包括: 检测是否接收到GPIO中断; 在接收到GPIO中断后,开始接收操作,并开启定时器; 在接收过程中,检测定时器是否中断; 如果有定时器中断,则确定接收完成,否则,继续接收数据。 通过上述流程可以看出,上述方式通过GPIO中断以及定时器完成模拟串行通信方 式。该方法通过GPIO中断检测数据接收的开始,然后通过定时器根据数据的波特率设置的 定时时间确定定时器中断的发生时间,通过定时器中断确定完成数据接收。 在实际应用中,采用上述方式有可能会导致数据接收以及发送失败。

技术实现要素:

为了解决上述任一技术问题,本申请实施例提供了一种嵌入式芯片中传输控制方 法和装置。 为了达到本申请实施例目的,本申请实施例提供了一种嵌入式芯片中传输控制方 法,包括: 确定通用型输入输出GPIO接口模拟的串行通信接口在传输单个比特时的通信时 长,得到单比特基准值; 在利用所述串行通信接口传输数据时,根据所述单比特基准值以及预先获取的需 传输的数据的比特数,判断传输操作是否完成,得到判断结果; 根据所述判断结果,对传输操作进行管理。 一种嵌入式芯片中传输控制装置,包括: GPIO接口,作为串行通信接口使用; 定时器,用于对所述串行通信接口传输数据的时间进行计时; 处理器,用于根据所述定时器的时间信息,执行上文所述的方法。 一种存储介质,所述存储介质中存储有计算机程序,其中,所述计算机程序被设置 为运行时执行上文所述的方法。 一种电子装置,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理 4 CN 111611186 A 说 明 书 2/6 页 器被设置为运行所述计算机程序以执行上文所述的方法。 上述技术方案中的一个技术方案具有如下优点或有益效果: 通过确定GPIO接口模拟的串行通信接口在传输单个比特时的通信时长,得到单比 特基准值,在利用所述串行通信接口传输数据时,根据所述单比特基准值以及预先获取的 需传输的数据的比特数,判断传输操作是否完成,得到判断结果,根据所述判断结果,对传 输操作进行管理,通过获取单比特基准值,可以消除由于芯片内部时钟差异性造成的固定 计数器计数值所带来的偏差,再利用该单比特基准值进行传输完成的判断,可以保证系统 的通信数据的准确传输,避免传输失败的发生。 本申请实施例的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明 书中变得显而易见,或者通过实施本申请实施例而了解。本申请实施例的目的和其他优点 可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。 附图说明 附图用来提供对本申请实施例技术方案的进一步理解,并且构成说明书的一部 分,与本申请实施例的实施例一起用于解释本申请实施例的技术方案,并不构成对本申请 实施例技术方案的限制。 图1为相关技术中利用软件模拟串行通信接口的接收方法的流程图; 图2为本申请实施例提供的嵌入式芯片中传输控制方法的流程图; 图3为本申请实施例提供的校准数据的传输的示意图; 图4为本申请实施例提供的数据接收方法的流程图; 图5为本申请实施例提供的嵌入式芯片中传输控制装置的结构图。