技术摘要:

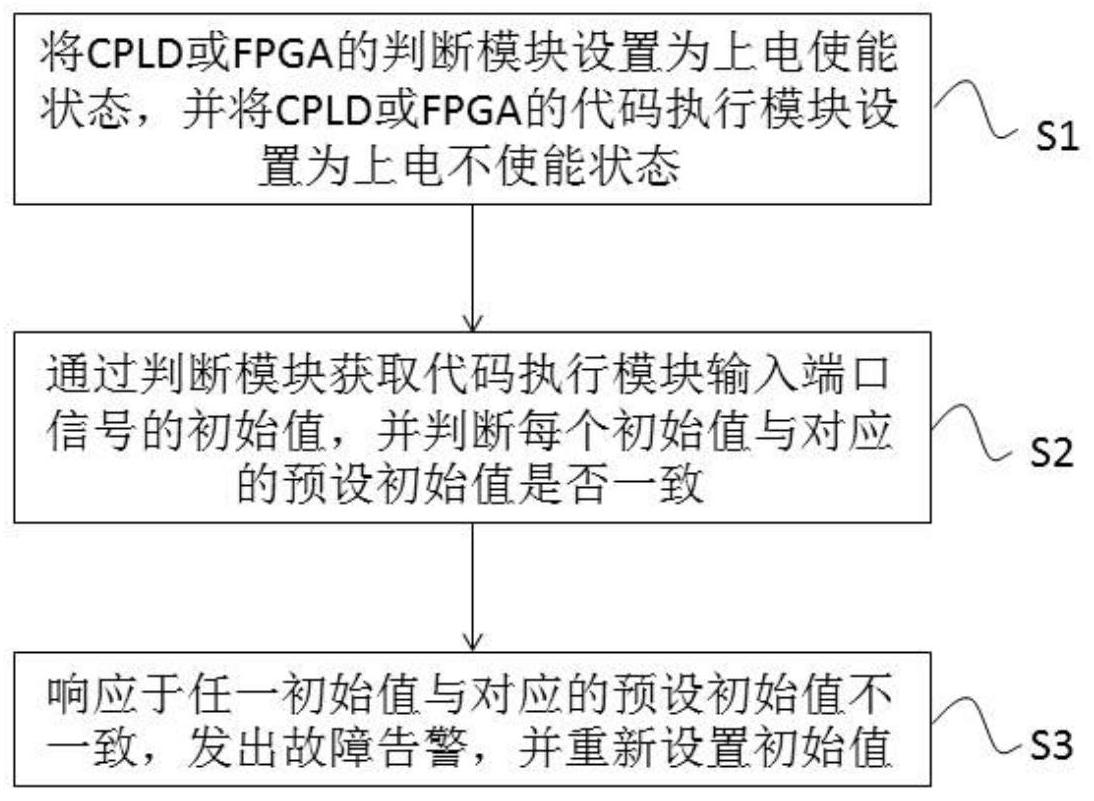

本发明公开了一种CPLD或FPGA信号处理的方法,包括以下步骤:将CPLD或FPGA的判断模块设置为上电使能状态,并将CPLD或FPGA的代码执行模块设置为上电不使能状态;通过判断模块获取代码执行模块输入端口信号的初始值,并判断每个初始值与对应的预设初始值是否一致;以及响 全部

背景技术:

服务器主板设计中均有设计CPLD或FPGA的应用,由于CPLD或FPGA可程序化的特 性,CPLD或FPGA非常广泛地被应用在服务器上,例如:服务器上的主板或背板及一些小板 卡,都会有CPLD或FPGA芯片的设计应用,而CPLD或FPGA在主板上的应用,主要是开启主板上 的电源芯片,监控一些主板上的状态或是接收从晶片来的控制讯号,并将该讯号经过CPLD 或FPGA内部逻辑的处理后,直接透传到后端的芯片。这表示在服务器中的设计有越来越多 的讯号都接到CPLD或FPGA芯片,并透过CPLD或FPGA内部可程序化的逻辑输出相关的控制讯 号,由于每一根进到CPLD或FPGA的输入讯号,都会有初始值的状态,假使外部初始值设计错 误,而将错误的讯号到CPLD或FPGA,将也会影响到CPLD或FPGA最后输出的逻辑结果,严重可 能导致无法开机或是系统异常误报警示。 在现有的服务器CPLD或FPGA设计中,大多CPLD或FPGA设计者都是直接将进入CPLD 或FPGA的讯号,经过CPLD或FPGA内部的同步处理后,直接将该讯号进到内部的逻辑判断,但 并没有针对当前输入到CPLD或FPGA的初始讯号判断是否正确,由于进入到CPLD或FPGA内部 讯号假使初始值的设定不对,原本初始值应该是低电平,却因为外部的电源电路设计错误, 芯片设计错误或是软件开发人员的设计错误导致,这样一个错误的讯号进入到CPLD或FPGA 判断后将会影响到CPLD或FPGA最后输出讯号的结果,严重的话将是导致没有办法开机,在 这样的情况下,需要耗费非常多的人力与时间才能找到问题。只要任何一根设定错误的初 始值进到CPLD或FPGA,就会为系统带来风险,轻则就是误报系统警示,自动关机或是无法开 机的严重行为。

技术实现要素:

有鉴于此,本发明实施例的目的在于提出一种CPLD或FPGA信号处理的方法、装置、 设备及可读介质,通过CPLD或FPGA内部的判断模块先确认外部信号的初始值是否正确,如 果发现初始值设计错误,告警并盘查所有信号的初始值,保证所有初始值全部正确才能启 动CPLD或FPGA内部代码,对信号进行同步处理,可以避免因为输入信号的初始值错误导致 CPLD或FPGA输出错误而影响系统运作,提高了CPLD或FPGA处理信号的效率。 基于上述目的,本发明实施例的一方面提供了一种CPLD或FPGA信号处理的方法, 包括以下步骤:将CPLD或FPGA的判断模块设置为上电使能状态,并将CPLD或FPGA的代码执 行模块设置为上电不使能状态;通过所述判断模块获取代码执行模块输入端口信号的初始 值,并判断每个初始值与对应的预设初始值是否一致;以及响应于任一初始值与对应的预 设初始值不一致,发出故障告警,并重新设置初始值。 在一些实施方式中,还包括:响应于全部初始值与对应的预设初始值均一致,使能 4 CN 111611135 A 说 明 书 2/6 页 代码执行模块,对信号进行同步处理。 在一些实施方式中,判断每个初始值与对应的预设初始值是否一致包括:判断初 始值电平高低与对应的预设初始值电平高低是否一致。 本发明实施例的另一方面,还提供了一种CPLD或FPGA信号处理的装置,包括:使能 模块,配置用于将CPLD或FPGA的判断模块设置为上电使能状态,并将CPLD或FPGA的代码执 行模块设置为上电不使能状态;初始值判断模块,配置用于通过所述判断模块获取代码执 行模块输入端口信号的初始值,并判断每个初始值与对应的预设初始值是否一致;以及处 理模块,配置用于响应于任一初始值与对应的预设初始值不一致,发出故障告警,并重新设 置初始值。 在一些实施方式中,处理模块进一步配置用于:响应于全部初始值与对应的预设 初始值均一致,使能代码执行模块,对信号进行同步处理。 在一些实施方式中,处理模块进一步配置用于:发出故障告警,并点亮故障输入端 口对应的LED灯;根据点亮的LED灯确定故障输入端口,并重新设置故障输入端口的初始值。 本发明实施例的再一方面,还提供了一种计算机设备,包括:至少一个处理器;以 及存储器,存储器存储有可在处理器上运行的计算机指令,指令由处理器执行时实现以下 步骤:将CPLD或FPGA的判断模块设置为上电使能状态,并将CPLD或FPGA的代码执行模块设 置为上电不使能状态;通过所述判断模块获取代码执行模块输入端口信号的初始值,并判 断每个初始值与对应的预设初始值是否一致;以及响应于任一初始值与对应的预设初始值 不一致,发出故障告警,并重新设置初始值。 在一些实施方式中,步骤还包括:响应于全部初始值与对应的预设初始值均一致, 使能代码执行模块,对信号进行同步处理。 本发明实施例的再一方面,还提供了一种计算机可读存储介质,计算机可读存储 介质存储有被处理器执行时实现如上方法步骤的计算机程序。 本发明具有以下有益技术效果:通过CPLD或FPGA内部的判断模块先确认外部信号 的初始值是否正确,如果发现初始值设计错误,告警并盘查所有信号的初始值,保证所有初 始值全部正确才能启动CPLD或FPGA内部代码,对信号进行同步处理,可以避免因为输入信 号的初始值错误导致CPLD或FPGA输出错误而影响系统运作,提高了CPLD或FPGA处理信号的 效率。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本 发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以 根据这些附图获得其他的实施例。 图1为本发明提供的CPLD或FPGA信号处理的方法的实施例的示意图。