技术摘要:

本发明公开一种插塞结构及其制作工艺,该插塞结构包含一第一介电层、一第二介电层、一阻障层以及一第二插塞。第一介电层位于一基底上,第一介电层具有一第一插塞位于其中,其中第一插塞连接位于基底中的一源/漏极。第二介电层位于第一介电层上,且第二介电层具有一开口 全部

背景技术:

在集成电路的制造过程中,场效晶体管(field effect transistor)是一种极重 要的电子组件,而随着半导体组件的尺寸越来越小,晶体管的制作工艺步骤也有许多的改 进,以制造出体积小而高品质的晶体管。现有的晶体管制作工艺是在基底上形成栅极结构 之后,再在栅极结构相对两侧的基底中形成轻掺杂漏极结构(lightly doped drain,LDD)。 接着于栅极结构侧边形成间隙壁(spacer),并以此栅极结构及间隙壁作为掩模,进行离子 注入步骤,以于基底中形成源极/漏极区。而为了要将晶体管的栅极、源极、与漏极适当电连 接于电路中,因此需要形成接触插塞(contact plug)来进行导通。接触插塞中更形成有阻 障层围绕其中的低电阻率材料以防止低电阻率材料向外扩散至其他区域。随着半导体组件 尺寸的缩小,在接触洞(contact hole)中填入阻障层以及低电阻率材料以形成接触插塞, 并维持甚至提升半导体组件的效能,即为目前业界发展的目标之一。

技术实现要素:

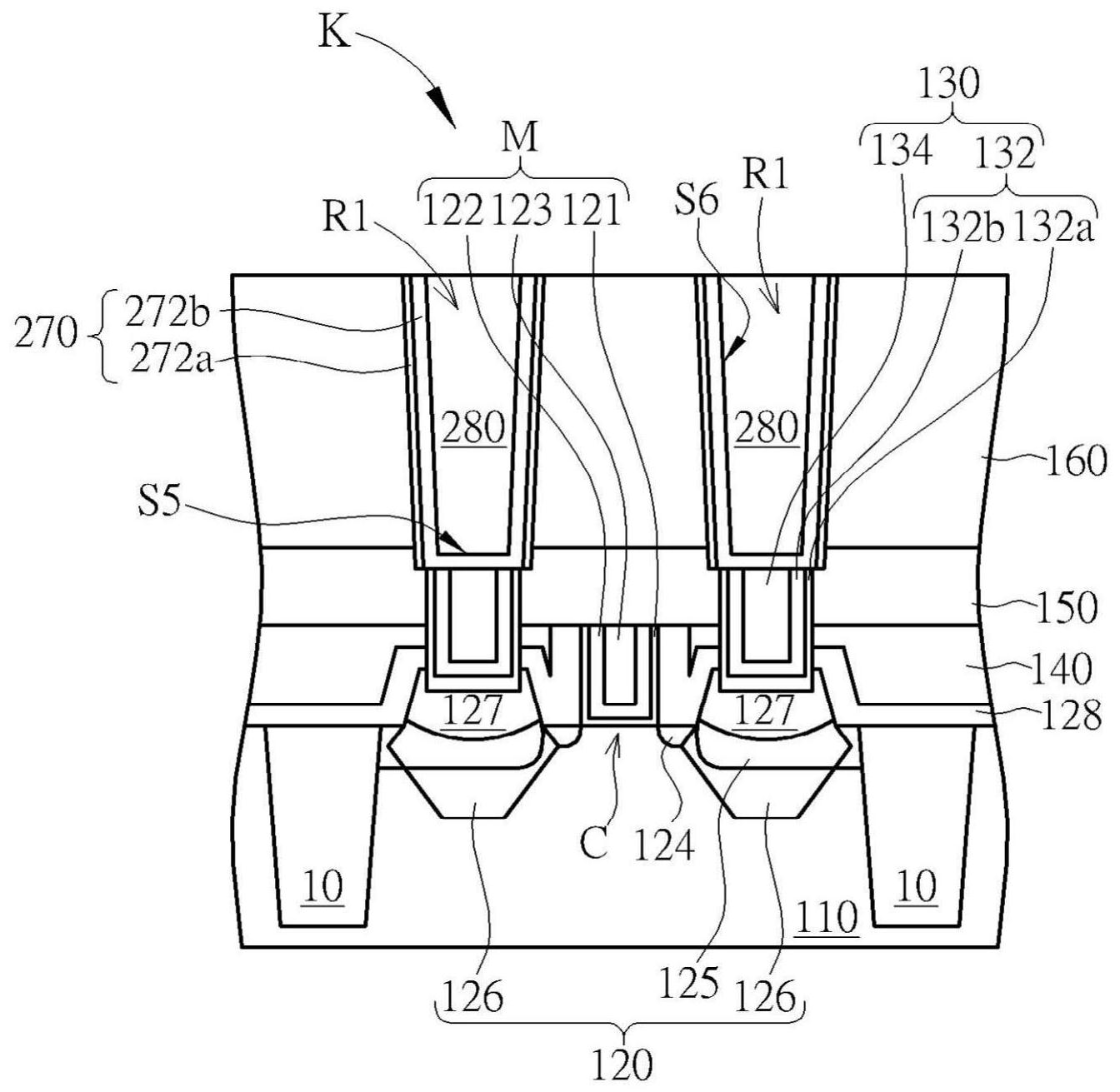

本发明的目的在于提供一种插塞结构及其制作工艺,其进行一溅镀制作工艺,移 除一阻障层的至少部分的底部,以提升所形成的半导体组件的电性品质。 为达上述目的,本发明提供一种插塞结构,包含一第一介电层、一第二介电层、一 阻障层以及一第二插塞。第一介电层位于一基底上,第一介电层具有一第一插塞位于其中, 其中第一插塞连接位于基底中的一源/漏极。第二介电层位于第一介电层上,且第二介电层 具有一开口暴露出第一插塞。阻障层顺应覆盖开口,其中阻障层具有一底部以及一侧壁部, 且底部为单层并连接第一插塞,而侧壁部为双层。第二插塞填满开口并位于阻障层上。 本发明提供一种形成插塞结构的制作工艺,包含下述步骤。首先,提供一基底,具 有一源/漏极。接着,依序形成一第一介电层以及一第二介电层于基底上,其中第一介电层 具有一第一插塞连接源/漏极,而第二介电层具有一开口暴露出第一插塞。接续,形成一阻 障层顺应覆盖开口以及第一插塞。续之,进行一第一溅镀制作工艺,移除至少部分阻障层的 一底部,但保留阻障层的一侧壁部。继之,形成一第二插塞于开口中。 基于上述,本发明提出一种插塞结构以及其形成制作工艺,其进行一第一溅镀制 作工艺以移除一阻障层的至少一层的一底部,因此可减少一第一插塞以及一第二插塞之间 的接触阻抗(contact resistance,Rc),提升第一插塞以及一第二插塞之间的粘着性,改善 阻障层的顶临界尺寸(critical dimension,CD)以及提升开口的填洞能力。 4 CN 111554659 A 说 明 书 2/6 页 附图说明 图1~图6是本发明第一实施例的形成插塞结构的制作工艺的剖面示意图; 图7~图10是本发明第二实施例的形成插塞结构的制作工艺的剖面示意图; 图11是本发明一实施例的插塞结构的剖面示意图; 图12是本发明一实施例的插塞结构的剖面示意图。 其中,附图标记说明如下: 10:绝缘结构 110:基底 120:MOS晶体管 121:介电层 122:功函数层 123:低电阻率材料 124:轻掺杂源/漏极 125:源/漏极 126:外延结构 128:接触洞蚀刻停止层 130:第一插塞 132、170、170’、270、370、470:阻障层 132a、172’a、172a、272’a、272a、372a、472a:钛层 132b、172’b、172b、272’b、272b、372b、472b:氮化钛层 134:低电阻率材料 140:第一介电层 150:盖层 160:第二介电层 180、280、380、480:第二插塞 180’:低电阻率材料 C:栅极通道 h1、h2:上表面 M:金属栅极 P1:第二溅镀制作工艺 P2:第一溅镀制作工艺 R1、R2、R3、R4:开口 S1、S3、S5:底部 S2、S4、S6:侧壁部 T1、T2:顶部