技术摘要:

本发明公开了一种高性能的抗干扰方法及装置,该方法包括:接收天线阵元信号,并进行预处理,得到带有相位和幅度信息的空域信号;根据接收的M个天线阵元空域信号,将每个天线阵元空域信号进行时域延迟,且每个天线阵元形成P个节点,从而把M个天线阵元空域信号转化为空时 全部

背景技术:

在卫星导航抗干扰领域,针对压制式干扰,采用阵列天线进行自适应调零,该技术 具有很好的干扰抑制效果。在工程中由于体积、成本及阵列天线的个数等因素受限,利用单 纯的空域调零技术无法满足复杂环境的作战要求,因为空域调零技术的自由度与其天线个 数有关,从而能够抑制的干扰数目也受到了天线个数的限制。面临日益复杂的干扰环境,通 常联合利用时域和空域的自由度来提高干扰抑制个数和抗干扰抑制能力,即空时联和抗干 扰技术。随着时域阶数的增加,其算法实现复杂度越来越高,因此就其算法实现成为了关注 的焦点,通常利用LMS迭代算法来简化工程实现复杂度,是目前常用的一种方法。但是LMS其 固有的缺点,首先是权值计算精度较差,无法逼近真实的解,从而影响该技术的抗干扰性 能,其次算法收敛速度慢,且受干扰样式和个数的影响,没有稳定的收敛时间,从而导致在 动态场景下其抗干扰性能下降。 为了达到空时联合抗干扰技术的最佳性能,采用矩阵求逆获得权值的处理方式是 最佳。该方法的优点是权值计算精度高,逼近真实解,其次收敛速度稳定,不受干扰样式和 个数的影响。但是矩阵求逆在硬件的实现中其计算时间会随着时域阶数的增加而导致实时 性很差,从而直接影响抗干扰技术的性能,无法满足工程应用的需要,失去其应用价值。

技术实现要素:

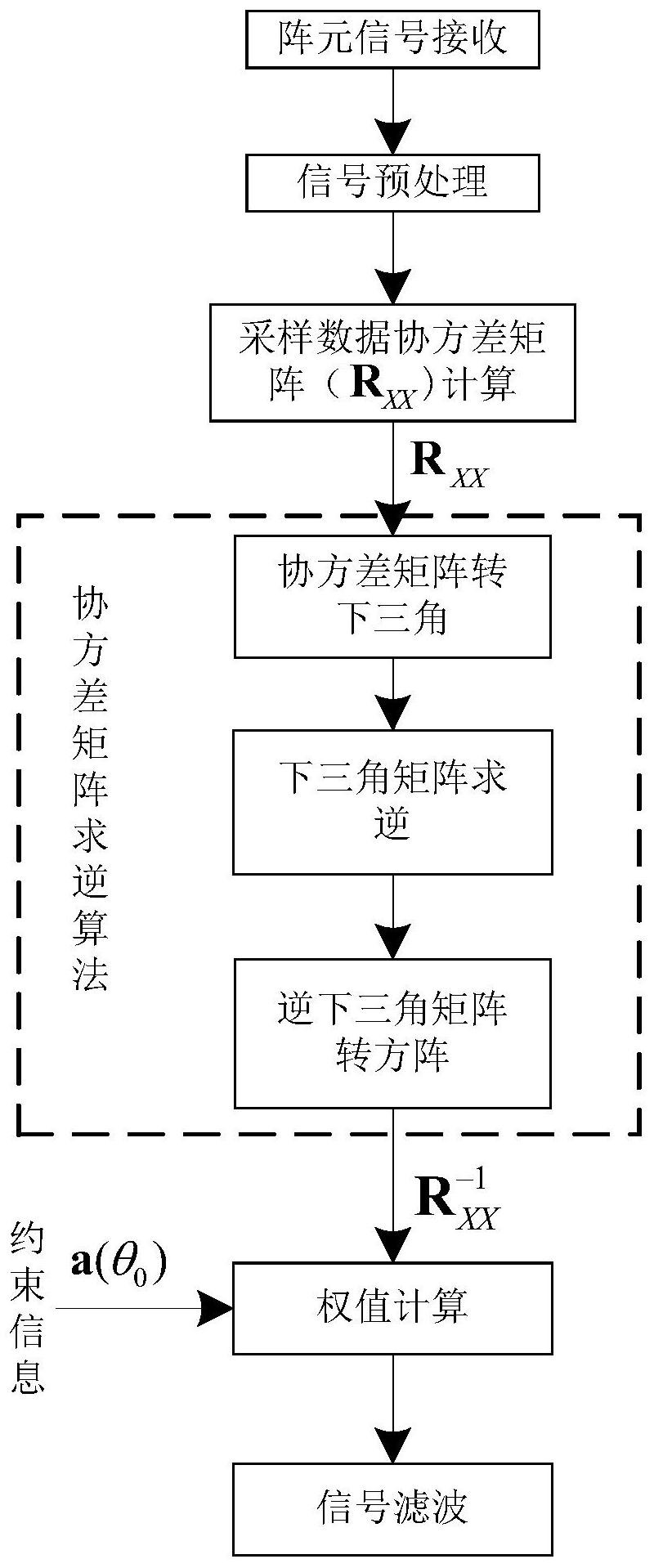

本发明所要解决的技术问题是目前常用的空时联合抗干扰技术的干扰抑制性能 差、精度不高问题,尤其在涉及的矩阵求逆硬件的实现方式是基于DSP硬件平台的实现方 式,但是该方式其计算速度较慢,特别是随着时域阶数的增加,其矩阵维数越来越大,很难 满足实时性要求从而影响其抗干扰性能,导致其基于DSP硬件平台的实现方式工程应用受 限。 本发明提供了解决上述问题的一种高性能的抗干扰方法及装置,本发明为了突破 基于硬件的大型矩阵求逆算法的问题,方案采用基于FPGA的硬件实现方式,在计算精度上 采用浮点的实现方式做到计算高精度,计算时间及资源上做到灵活配置,使得工程应用高 效合理。 本发明通过下述技术方案实现: 一种高性能的抗干扰方法,包括以下步骤: S1:接收天线阵元信号,并进行预处理,得到带有相位和幅度信息的IQ空域信号; S2:根据步骤S1接收的M个天线阵元空域信号,将每个天线阵元空域信号进行时域 延迟,且每个天线阵元形成P个节点,从而把M个天线阵元空域信号转化为空时信号X=[x11 x12 … xMP]′,其中′表示转秩运算; 6 CN 111596320 A 说 明 书 2/11 页 S3:根据步骤S2生成的空时信号生成采样数据协方差矩阵RXX,并进行采样数据协 方差矩阵RXX的计算; S4:根据步骤S3获得的采样数据协方差矩阵RXX,采用改进的协方差矩阵求逆算法 对采样数据协方差矩阵RXX进行求逆运算,得到 S5:根据约束信息a(θ0)和协方差矩阵的逆 计算权值,计算公式如下: 式中wopt为待滤波信号的权值;a(θ0)为约束信息,a(θ0)=[1 0 ... 0]′;aH(θ0)为 a(θ0)的共轭转秩; S6:根据权值信息和信号进行滤波处理,最终输出抗干扰之后的滤波输出信号Y; 其中,滤波输出信号Y计算公式如下: 式中 为待滤波信号的权值的共轭转秩,X为空时信号,且X=[x11 x12 … xMP]′。 工作原理如下: 空时联合抗干扰技术理论上采用基于采样协方差矩阵求逆的算法实现,其计算结 果最逼近真实的解来,一方面极大地减少了实现带来的误差影响因素,其次与采用LMS开环 迭代的实现方式不一样,此实现方式是一个闭环求解过程,收敛速度稳定,只依赖于算法的 计算时间延迟,不受干扰样式和个数的影响,避免了外界干扰场景变化带来的收敛速度不 稳定的影响因素。从上分析可知采用基于采样协方差矩阵求逆的算法实现优点是求解精度 高,逼近理论结果,其次收敛速度稳定,动态变化场景下性能稳定,极大提升空时联合抗干 扰技术的干扰抑制性能。因此如何实现基于硬件的大型矩阵求逆算法是其关键,在满足计 算精度的同时还需满足其实时性。 为了弥补上述技术的缺点,采用FPGA来实现矩阵求逆算法,突破其工程应用的瓶 颈,满足高精度高实时性能,从而使得空时联合抗干扰技术的性能达到最优,提升了抗干扰 整体性能,又能使其工程可用,打破常规的利用DSP来实现矩阵求逆算法的问题,随着矩阵 维数的增加其计算速度相对DSP有着巨大的优势,并且FPGA的设计可以在计算精度、速度及 硬件资源上取得一个平稳,有着DSP无法可比的优势。 为了突破基于硬件的大型矩阵求逆算法的问题,本发明采用基于FPGA的硬件实现 方式,在计算精度上采用浮点的实现方式做到计算高精度,计算时间及资源上做到灵活配 置,使得工程应用高效合理。 进一步地,步骤S3中采样数据协方差矩阵RXX的计算,是采用采样数据非连续采样 点进行流水设计处理,通过设置间距参数来控制;其中,采样间距设置为M*P。 进一步地,步骤S3包括以下子步骤: 步骤3.1:把步骤S2得到的空时信号进行互相关相乘处理得到一个采样时刻形成 的互相关矩阵,计算方式为X*XH,其中XH表示X的共轭转秩; 步骤3.2:根据步骤3.1得到的互相关矩阵,选取L个非连续的样点,间隔设置为M* 7 CN 111596320 A 说 明 书 3/11 页 P; 步骤3.3:进行样点数据累加,并求平均,得到S=M*P维协方差矩阵RXX。 进一步地,步骤S4包括以下子步骤: 步骤4.1:把步骤S3得到的协方差矩阵RXX转换为下三角矩阵,具体包括: 步骤4.1.1:将协方差矩阵RXX数据的实部和虚部进行拼接,S维复矩阵转变为2S维 实矩阵; 步骤4.1.2:将拼接后的数据缓存在FPGA编程器件中的块RAM存储器中; 步骤4.1.3:将RAM存储器缓存后的数据进行重组,得到2S维实矩阵的下三角矩阵; 步骤4.2:对步骤4.1得到的下三角矩阵进行下三角求逆算法; 步骤4.3:根据步骤4.2得到的逆下三角矩阵,对其进行转方阵处理,得到逆矩阵; 具体包括: 步骤4.3.1:将逆下三角阵数据缓存于RAM存储器中; 步骤4.3.2:将缓存数据进行重组,得到方阵的实部和虚部,即 进一步地,步骤4.2具体包括以下子步骤: 步骤4.2.1:将步骤4.1中下三角矩阵的整型输入数据元素转为浮点数据,存储在 浮点矩阵A中;转步骤4.2.3; 步骤4.2.2:变量k[n](n=1,2,…,N)初始化,k[n]=2S-N*(n-1);转步骤4.2.3; 步骤4.2.3:采用N个并行浮点求逆设计,其中N表示参数,根据硬件资源进行灵活 配置,满足1≤N≤2S都是有效参数;具体为: 步骤4.2.3.1:变量k[n]分发控制,当第一次迭代时接受步骤4.2.2的数据,后面迭 代时接受步骤4.2.6的数据; 步骤4.2.3.2:进行N个浮点输入模块的数据更新;对第1个数据更新,当第一次迭 代时接受步骤4.2.1的数据作为后面迭代时第1个数据更新接受第N 1个更新数据;对n=2, 3,..,N 1将第n-1个浮点求逆模块的输出作为第n个数据更新; 步骤4.2.3.3:当N个浮点求逆模块的输入数据更新和变量k[n](n=1,2,…,N)都 全部更新完成后,对第n(n=1,2,…,N)个求逆模块;转步骤4.2.4; 步骤4.2.4:进行浮点求逆处理,具体为: 步骤4.2.4.1:矩阵奇异判定:当A(1,1)=0时给出奇异标志,否则转步骤4.2.4.2; 步骤4.2.4 .2:取出输入数据A(1 ,1),计算p=1/A(1 ,1),完成浮点除法;转步骤 4.2.4.3; 步骤4.2.4.3:循环变量i初始化,i=2;执行如下: 步骤4.2.4.3.1:将矩阵存在RAM存储器中,q=A(i,1),计算qp=q*p,完成浮点乘 法,转步骤4.2.4.3.2; 步骤4.2.4 .3 .2:判断i与k,计算h;当i>=k时,h=qp;当i