技术摘要:

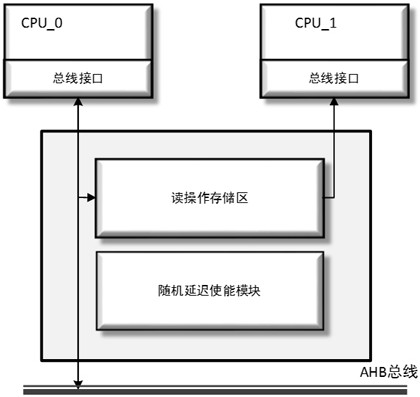

本发明涉及微控制器领域,提出了一种双核锁步容错下的处理器抗DPA攻击系统包括主处理器和从处理器,还包括随机延迟使能模块和读操作存储区;所述随机延迟使能模块用于控制从处理器的随机延迟;所述读操作存储区用于存储主处理器读取过的指令和数据,提供从处理器正确的 全部

背景技术:

随着工业4.0时代的到来,微控制器在我国工业自动化发展中正扮演着越来越重 要的角色。处理器作为微控制器的核心,由于不断更新的工艺节点以及不断发展的攻击技 术,其可靠性和安全性正面临着严峻的挑战。在可靠性方面,目前针对商用处理器的主流容 错方法之一是双核锁步容错方案。该技术通过采用两个处理器,使其成为自监控对,检测故 障的发生。通常,会结合检查点技术,在软件上进行状态保存和状态恢复,能够在检测故障 的同时,完成故障恢复。在安全性方面,目前较为流行的一种攻击方式是差分功耗分析攻击 (DPA),这是一种通过分析硬件运算时泄露的功耗信息获取密钥的攻击方式,由于它绕过对 加密算法本身的繁琐分析,直接着手功耗与数据间的相关性分析,因而能够快速准确地获 取密钥。对于处理器来说,当其进行软件加密时,内部的处理器在执行加密算法时,攻击者 可以通过功耗与指令及数据间的相关性,结合统计数据分析获取密钥。在毫无保护的设备 上,这种攻击方式能够以低廉的攻击成本快速获得密钥,进而获取敏感信息,从而带来灾难 性的后果。目前,针对处理器的抗攻击防护中已有的一些方法,如在CPU的流水架构中插入 一些随机指令或延迟等待的方式,破坏功耗与加解密算法间的相关性。然而,对于需要同时 实现双核锁步容错的处理器来说,这些不受控制的随机延迟会直接导致双核锁步容错功能 的失效。此外,这些方法需要对嵌入式CPU内部架构进行修改,处理器内部的逻辑极为复杂, 牵一发则动全身,对于不熟悉处理器结构和内部实现细节的人来说,修改处理器的代价较 大。

技术实现要素:

为了解决现有技术中存在的上述技术问题,本发明提供一种双核锁步容错下的处 理器抗DPA攻击系统,其具体技术方案如下。 一种双核锁步容错下的处理器抗DPA攻击系统包括主处理器、从处理器、随机延迟 使能模块和读操作存储区;所述随机延迟使能模块用于控制从处理器的随机延迟;所述读 操作存储区用于存储主处理器读取过的指令和数据,提供给从处理器正确的指令和数据; 所述主处理器和从处理器在运行中包括同步运行阶段和失步运行阶段。 进一步的,所述同步运行阶段为主处理器和从处理器间的运行状态一致,所述失 步运行阶段为主处理器和从处理器间的运行状态不一致。 进一步的,所述主处理器和从处理器处于失步运行阶段时,所述从处理器随机插 入延时,所述主处理器通过在写操作前随机插入延时以等待与从处理器同步运行;所述延 时通过拉低AHB总线上的hready信号来实现。 进一步的,所述延时通过拉低AHB总线上的hready信号来实现具体包括:当所述 4 CN 111581676 A 说 明 书 2/3 页 hready信号为低时,主处理器和从处理器会停在当前指令周期,所述hready信号为高电平 时,完成当前指令,往下执行程序。 进一步的,所述随机延迟使能模块发出随机延迟使能信号,所述随机延迟使能信 号包括高电平的随机延迟使能信号和低电平的随机延迟使能信号,通过真随机数、计数器 和相关控制逻辑获得;所述真随机数通过真随机数发生器获得,然后经掩码后的数据为 rand_num;所述控制逻辑发出抗DPA使能信号。 进一步的,当所述抗DPA使能信号为高电平时,所述计数器对所述rand_num进行计 数,当计数至0时,随机延迟使能信号电平拉高;然后再次获得rand_num进行计数,当计数至 0时,随机延迟使能信号电平拉低。 进一步的,所述读操作存储区设有6个深度为16的FIFO存储器,分为3组,第一组为 数据FIFO存储器,其中的2个FIFO存储器用于存储读取的数据和对应的地址;第二组为指令 FIFO存储器,其中的2个FIFO存储器用于存储读取的指令和对应的地址;第三组为常量FIFO 存储器,其中的2个FIFO存储器用于存储读取的常量和对应的地址。 进一步的,所述主处理器将读取过的指令和数据写入到所述FIFO存储器中,失步 运行后的从处理器读取的指令和数据从所述FIFO存储器中获得。 进一步的,所述随机延迟使能信号为高电平时或从处理器的运行状态追上主处理 器的运行状态,即读操作存储区中的FIFO中的指令和数据为空时,所述从处理器进行延迟 操作,进入失步运行状态;反之,所述从处理器恢复运行,从读操作存储区中获得读操作请 求的指令和数据。 进一步的,在失步运行阶段,所述读操作存储区中的FIFO满时或主处理器执行写 操作时,所述主处理器进行延迟操作,直到从处理器执行到所述写操作。 有益效果: 本发明的双核锁步容错下的处理器抗DPA攻击系统,通过总线层面的修改,在保证原有 双核锁步正常工作的同时,进行时间及振幅维度上的双重功耗隐藏,以实现双核锁步容错 下的处理器的抗DPA攻击特性。 附图说明 图1为本发明的双核锁步容错下的抗DPA攻击设计框图; 图2为本发明的主处理器和从处理器同步与失步运行示意图; 图3为本发明的随机延迟使能模块结构图; 图4为本发明的读操作存储区框图。