技术摘要:

本发明公开了一种ADC芯片测试电路和设备,包括计数器;数据比较模块,分别与计数器和待测芯片连接,控制端连接有第一预处理模块,第一预处理模块与计数器连接,数据比较模块连接有第二预处理模块,第一预处理模块用于检测数字码的极值并给所述数据比较模块发送补位使能 全部

背景技术:

现有的模数转换芯片(Analog-to-digital converter,以下简称ADC芯片)的测试 电路通常采用高精度和高稳定度的模拟信号源。在测试时,待测芯片的输入端连接有高精 度和高稳定度的模拟信号源,待测芯片的输出端连接有高速比较器,高速比较器在同步时 钟的控制下以高于模数转换速率数倍的采样速率进行多次采样,并交给后级的DSP或PC进 行数字信号和噪声处理。 然而,现有的测试电路存在一些问题,例如,高精度和高稳定度的模拟信号源通常 具有高精度的数模转换器(Digital-to-analog converter,DAC),成本较高。由于高精度 DAC的输出端驱动能力不足,在实际使用时必须后接放大输出电路,因此会引入噪声干扰, 而且后级放大输出会带来漂移效应,导致设定的电压与实际输出的电压存在偏差,因而加 大了电路设计难度、增加了电路设计成本。

技术实现要素:

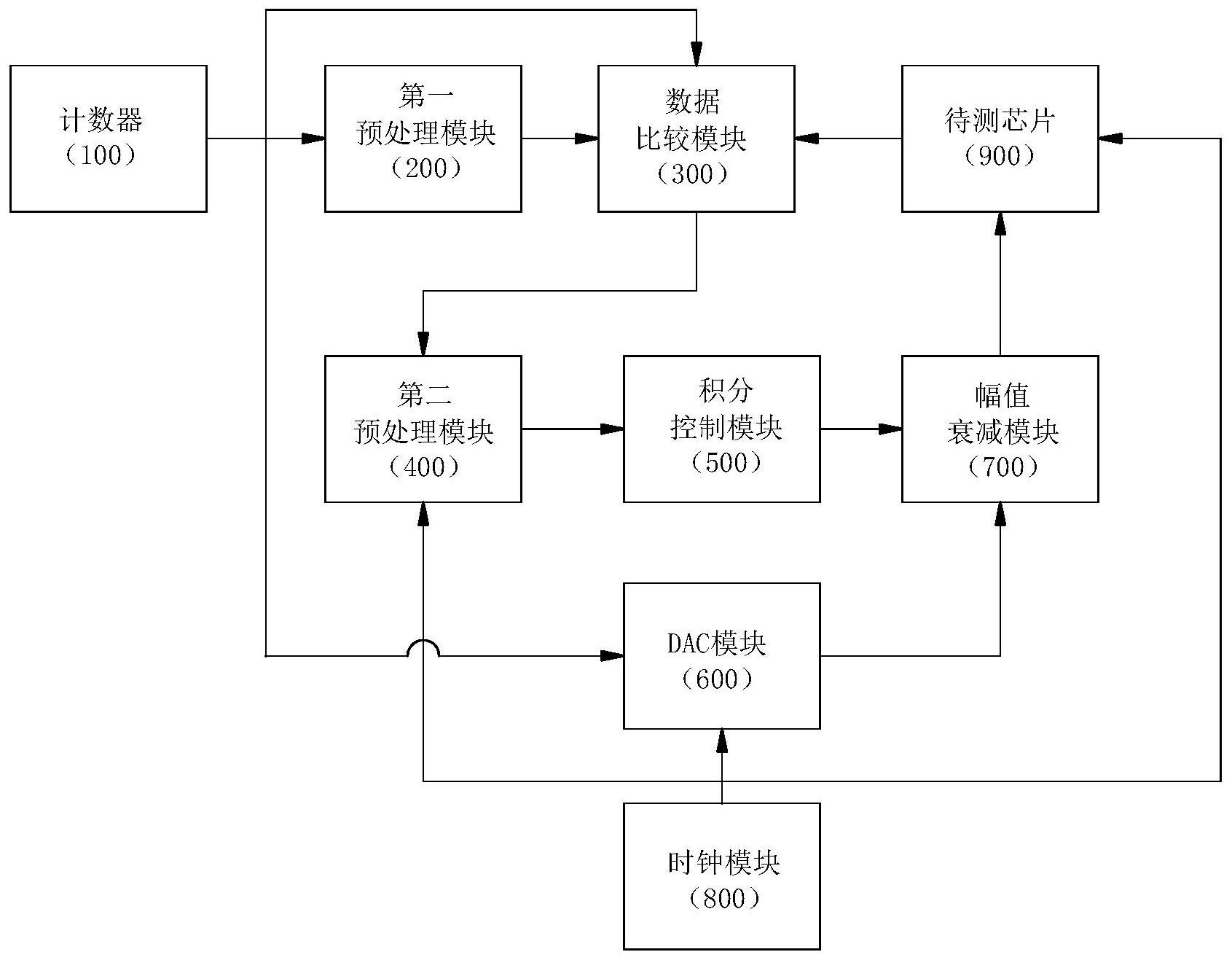

本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出一种ADC 芯片测试电路,利用成本较低的器件进行ADC芯片测试,降低测试成本。 第一方面,根据本发明实施例的ADC芯片测试电路,包括计数器,用于输出数字码; 数据比较模块,具有第一输入端、第二输入端、控制端和输出端,所述数据比较模块的第一 输入端与所述计数器连接,所述数据比较模块的第二输入端与待测芯片的输出端连接,所 述数据比较模块的控制端连接有第一预处理模块,所述第一预处理模块的输入端与所述计 数器连接,所述数据比较模块的输出端连接有第二预处理模块,所述第一预处理模块用于 检测所述数字码的极值并给所述数据比较模块发送补位使能信号,所述第二预处理模块用 于保持所述数据比较模块的输出信号稳定;积分控制模块,与所述第二预处理模块的输出 端连接;DAC模块,输入端与所述计数器连接;幅值衰减模块,具有第一输入端、第二输入端 和输出端,所述幅值衰减模块的第一输入端与所述积分控制模块的输出端连接,所述幅值 衰减模块的第二输入端与所述DAC模块的输出端连接,所述幅值衰减模块的输出端用于连 接所述待测芯片的输入端;时钟模块,输出端分别与所述第二预处理模块、所述DAC模块和 所述待测芯片的时钟信号端连接。 根据本发明的一些实施例,所述第一预处理模块包括极大值检测电路和极小值检 测电路,所述极大值检测电路的输入端和所述极小值检测电路的输入端分别与所述计数器 连接,所述极大值检测电路的输出端和所述极小值检测电路的输出端分别与所述数据比较 模块连接,所述极大值检测电路用于检测所述数字码是否为极大值,并根据检测结果输出 第一补位使能信号,所述极小值检测电路用于检测所述数字码是否为极小值,并根据检测 结果输出第二补位使能信号。 4 CN 111579963 A 说 明 书 2/8 页 根据本发明的一些实施例,所述极大值检测电路包括第一或非门和至少一个第一 与非门,所述第一与非门的输入端与所述计数器连接,所述第一与非门的输出端与所述第 一或非门连接,所述第一或非门的输出端与所述数据比较模块连接。 根据本发明的一些实施例,所述极小值检测电路包括第二或非门、多个第一反相 器和至少一个第二与非门,多个所述第一反相器的输入端分别与所述计数器连接,多个所 述第一反相器的输出端分别与对应的所述第二与非门连接,所述第二与非门的输出端与所 述第二或非门连接,所述第二或非门的输出端与所述数据比较模块连接。 根据本发明的一些实施例,所述数据比较模块包括多个级联连接的数值比较芯 片,所述数值比较芯片具有第一输入端、第二输入端、级联输入端和输出端,每一级所述数 值比较芯片的第一输入端用于分别与所述计数器连接,每一级所述数值比较芯片的第二输 入端分别与所述待测芯片的输出端连接,前一级所述数值比较芯片的输出端与后一级所述 数值比较芯片的级联输入端连接,第一级所述数值比较芯片的级联输入端作为所述数据比 较模块的控制端,最后一级所述数值比较芯片的输出端作为所述数据比较模块的输出端。 根据本发明的一些实施例,所述数据比较模块还包括第一双向可控开关和第二反 相器,所述第一双向可控开关具有常闭端、常开端、静端和控制端,所述第一双向可控开关 的常开端与所述第二反相器的输出端连接,所述第一双向可控开关的常闭端和所述第二反 相器的输入端分别用于接收来自所述待测芯片的数字码的最高位信号,所述第一双向可控 开关的静端与所述数据比较模块的最后一级数值比较芯片的第二输入端连接,所述第一双 向可控开关的控制端用于接收第一切换控制信号。 根据本发明的一些实施例,所述第二预处理模块包括RS触发器和至少两个D触发 器,至少两个所述D触发器的输入端分别与所述数据比较模块输出端连接,至少两个所述D 触发器的反相输出端分别与所述RS触发器的输入端连接,所述RS触发器的同相输出端与所 述积分控制模块连接。 根据本发明的一些实施例,所述第二预处理模块还包括第二双向可控开关,所述 第二双向可控开关具有常闭端、常开端、静端和控制端,所述第二双向可控开关的常闭端和 常开端分别与所述RS触发器的两个输出端连接,所述第二双向可控开关的静端与所述积分 控制模块的输入端连接,所述第二双向可控开关的控制端用于接收第二切换控制信号。 根据本发明的一些实施例,所述幅值衰减模块包括第一运放,所述第一运放的同 相输入端连接有电阻R9,并通过所述电阻R9与所述积分控制模块连接,所述第一运放的同 相输入端还连接有电阻R8和电阻R7,所述电阻R7的一端与所述电阻R8连接,所述电阻R7的 另一端接地,所述电阻R7和所述电阻R8之间的连接节点还与所述DAC模块的输出端连接。 第二方面,根据本发明实施例的ADC芯片测试设备,包括上述的ADC芯片测试电路。 根据本发明实施例的一个或多个技术方案,至少具有如下有益效果:与现有技术 中高精度高稳定度的模拟信号源相比,本发明采用成本较低的计数器和DAC模块,通过时钟 模块同步驱动待测芯片和DAC模块,通过调整计数器和时钟模块之间的频率关系,可以实现 微秒级测量,第一预处理模块通过输出补位使能信号可以实现待测芯片零点和满量程点的 稳定测量,第二预处理模块可以保持数据比较模块的输出芯片稳定,有利于降低各模块对 元器件的精度要求,从而降低电路成本。 本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变 5 CN 111579963 A 说 明 书 3/8 页 得明显,或通过本发明的实践了解到。 附图说明 本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得 明显和容易理解,其中: 图1为本发明实施例的ADC芯片测试电路的原理框图; 图2为本发明实施例的ADC芯片测试电路的极大值检测电路的电路原理图; 图3为本发明实施例的ADC芯片测试电路的极小值检测电路的电路原理图; 图4为本发明实施例的ADC芯片测试电路的数据比较模块的电路原理图之一; 图5为本发明实施例的ADC芯片测试电路的第二预处理模块的电路原理图之一; 图6为本发明实施例的ADC芯片测试电路的计数器的电路原理图; 图7为本发明实施例的ADC芯片测试电路的第一预处理模块的电路原理图; 图8为本发明实施例的ADC芯片测试电路的数据比较模块的电路原理图之一; 图9为本发明实施例的ADC芯片测试电路的第二预处理模块的电路原理图之一; 图10为本发明实施例的ADC芯片测试电路的积分控制模块的电路原理图; 图11为本发明实施例的ADC芯片测试电路的幅值衰减模块的电路原理图; 图12为本发明实施例的ADC芯片测试电路的DAC模块的电路原理图。