技术摘要:

本发明公开了一种低功耗基准电压和基准电流产生电路,包括启动电路、基准电流产生模块和基准电压产生模块。启动电路注入电流脉冲,使电路脱离零状态;基准电压作为基准电流产生模块的输入信号,控制基准电流产生电路中工作在深线性区的MOS管的输出电阻的温度系数来产生 全部

背景技术:

基准电压与基准电流是模拟电路设计和数模混合设计中基本模块单元,降低其功 耗是非常有意义的。此外,传统带隙基准电压源和现有的低功耗基准电压源总电流随温度 增加而增加。目前同时产生基准电压和基准电流主要有两种方案:一是先产生基准电压,然 后通过带电阻的电压转换电流电路,因此,降低功耗需要大电阻,增加芯片面积。同时电压 转换电流电路也会消耗一部分功耗;二是完全独立产生基准电压和基准电流,这会增加电 路消耗电流支路的数量。现有技术中,尚无低功耗且同时产生基准电压和基准电流的电路。

技术实现要素:

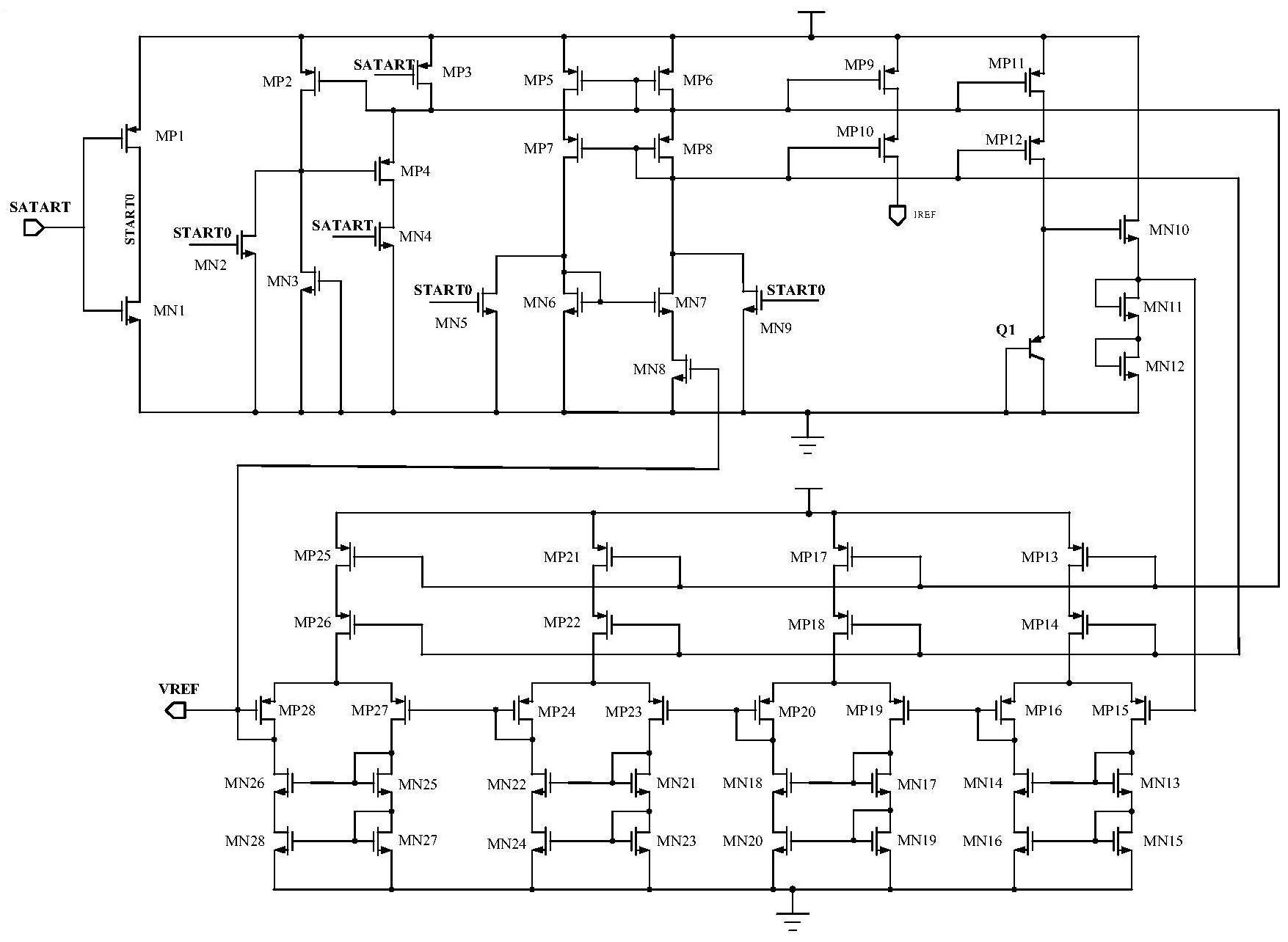

本发明提供了一种低功耗基准电压和基准电流产生电路,不仅能够解决传统产生 基准电压和基准电流电路需要较多消耗功耗支路和更大芯片面积的问题,还克服了传统带 隙基准电压源和现有的低功耗基准电压源总电流随温度增加而增加的缺点。 为了达到上述目的,本发明提供如下技术方案: 一种低功耗基准电压和基准电流产生电路,包括启动电路、基准电流产生模块和 基准电压产生模块;所述启动电路与基准电流产生模块相连,使其产生电流脉冲以脱离零 状态;所述基准电流产生模块与基准电压产生模块相连并为其提供工作电流;所述电压产 生模块的输出基准电压作为基准电流产生模块的输入信号,控制该模块中的MOS电阻温度 系数从而产生基准电流; 所述启动电路包括第一PMOS管、第一NMOS管、第二NMOS管、第二PMOS管、第三NMOS 管、第三PMOS管、第四PMOS管、第四NMOS管、第五NMOS管、第九NMOS管;所述第一PMOS管的栅 极接启动开关START,其源级接电源且漏极接节点START0;所述第一NMOS管的栅极接启动开 关START,其源级接地且漏极接节点START0;所述第二NMOS管的栅极接节点START0,其源极 接地且漏极接第二PMOS管的漏极、第三NMOS管的漏极和第四PMOS管的栅极;所述第二PMOS 管的源级接电源;所述第三NMOS管的源极和栅极接地;所述第三PMOS管的栅极接启动开关 START,其源级接电源;所述第四PMOS管的漏极接第四NMOS管的漏极;所述第四NMOS管的栅 极接启动开关START,其源级接地;所述第五NMOS管和第九NMOS管的栅极都接节点START0, 源级都接地; 所述基准电流产生模块包括第五PMOS管、第六PMOS管、第七PMOS管、第八PMOS管、 第六NMOS管、第七NMOS管、第八NMOS管、第九PMOS管、第十PMOS管;所述第五PMOS管的栅极接 第二PMOS管的栅极、第三PMOS管的漏极、第四PMOS管的源极、第六PMOS管的栅级与漏极、第 八PMOS管的源极和第九PMOS管的栅极,第五PMOS管的源极接电源且漏极接第七PMOS管的源 极;所述第六PMOS管的源极接电源;所述第七PMOS管的栅极接第八PMOS管的栅极与漏极、第 七NMOS管的漏极、第九NMOS管的漏极和第十PMOS管的栅极,第七PMOS管的漏极接第五NMOS 4 CN 111552342 A 说 明 书 2/5 页 管的漏极、第七NMOS管的栅极和第六NMOS管的栅极与漏极;所述的第六NMOS管的源极接地; 所述第七NMOS管的源极接第八NMOS管的漏极;所述第八NMOS管的栅极接输出基准电压 VREF,其源极接地;所述第九PMOS管的源极接电源,其漏极接第十PMOS管的源极;所述第十 POMS管的漏极接输出基准电流IREF; 所述基准电压产生模块包括分压电路和正温度系数电压产生电路;所述分压电路 获取2/3倍的PN结电压,分压电路的输出作为正温度系数电压产生模块的输入信号以获得 近似零温度系数的基准电压;所述分压电路包括第十一PMOS管、第十二PMOS管、第一PNP管、 第十NMOS管、第十一NMOS管、第十二NMOS管;所述第十一PMOS管的栅极接第九PMOS管的栅 极,其源极接电源且漏极接第十二PMOS管的源极;所述第十二PMOS管的栅极接第十PMOS管 的栅极,其漏极接所述第十NMOS管的栅极和第一PNP管的发射极;所述第一PNP管的基极和 集电极接地;所述第十NMOS管的漏极接电源,其源极接第十一NMOS管的栅极与漏极;所述第 十一NMOS管的源极接第十二NMOS管的栅极与漏极;所述第十二NMOS管的源极接地;所述正 温度系数电压产生电路包括若干个串联的子电路;每个子电路包括第十三PMOS管、第十四 PMOS管、第十五PMOS管、第十六PMOS管、第十三NMOS管、第十四NMOS管、第十五NMOS管、第十 六NMOS管;所述第十三PMOS管的源极接电源,其漏极接第十四PMOS管的源极,第十三PMOS管 的栅极接第十一PMOS管的栅极;所述第十四PMOS管的漏极接第十五PMOS管的源极和第十六 PMOS管的源极,第十四PMOS管的栅极接第十二PMOS管的栅极;所述第十五PMOS管的漏极接 第十四NMOS管的栅极和第十三NMOS管的栅极与漏极;所述第十六PMOS管的栅极与漏极接第 十四NMOS管的漏极;所述第十三NMOS管的源极接第十六NMOS管的栅极和第十五NMOS管的栅 极与漏极;所述第十四NMOS管的源极接第十六NMOS管的漏极;所述第十五NMOS管和第十六 NMOS管的源极都接地;第一个所述子电路中的第十五PMOS管的栅极接分压电路中的第十 NMOS管的源极,除第一个所述子电路外的各所述子电路的第十五PMOS管的栅极与前一个所 述子电路中的第十六PMOS管的栅极相连,最后一个所述的子电路中第十六PMOS管的栅极为 输出基准电压VREF。 进一步的,所述的基准电流产生模块和基准电压产生模块中,除第八NMOS管外,其 余NMOS管和PMOS管均工作在亚阈值区;第八NMOS管工作在深线性区。 进一步的,所述的基准电流作为基准电压产生电路的工作电流;所述的基准电压 作为基准电流模块的输入信号,控制基准电流模块中作为MOS电阻的第八NMOS管输出电阻 的温度系数,构成一个闭环结构。 进一步的,所述的第十NMOS管、第十一NMOS管和第十二NMOS管的尺寸相同。 进一步的,所述的第十五PMOS管的栅极电压为第一PNP管的发射极与基极电压差 的2/3。 与现有技术相比,本发明具有如下优点和有益效果: 1 .克服传统带隙基准电压源和现有低功耗基准电压源功耗随温度增加而增加的 缺点,在宽温度范围内,电路总功耗基本不变。 2.单电路同时产生基准电压和基准电流,降低具有基准电压和基准电流的电路支 路数目,降低芯片的功耗。 5 CN 111552342 A 说 明 书 3/5 页 附图说明 图1为本发明提供的低功耗基准电压和基准电流产生电路的电路图。 图2为本发明基准电流产生模块的电路图。 图3为本发明分压电路的电路图。 图4为本发明正温度系数电压产生电路的子电路的电路图。