技术摘要:

一种半导体结构及其形成方法,形成方法包括:提供鳍部和位于所述鳍部上的沟道叠层,沟道叠层包括牺牲层和位于牺牲层上的沟道层,靠近鳍部一侧的部分沟道层作为第一沟道层,位于第一沟道层上的剩余沟道层作为第二沟道层;形成多个横跨沟道叠层的伪栅结构;在伪栅结构两 全部

背景技术:

在半导体制造中,随着超大规模集成电路的发展趋势,集成电路特征尺寸持续减 小,为了适应更小的特征尺寸,金属-氧化物半导体场效应晶体管(Metal-Oxide- Semiconductor Field-Effect Transistor,MOSFET)的沟道长度也相应不断缩短。然而,随 着器件沟道长度的缩短,器件源极与漏极间的距离也随之缩短,因此栅极结构对沟道的控 制能力随之变差,栅极电压夹断(pinch off)沟道的难度也越来越大,使得亚阈值漏电 (subthreshold leakage)现象,即所谓的短沟道效应(SCE:short-channel effects)更容 易发生。 因此,为了更好的适应器件尺寸按比例缩小的要求,半导体工艺逐渐开始从平面 晶体管向具有更高功效的三维立体式的晶体管过渡,如全包围栅极(Gate-all-around, GAA)晶体管。全包围金属栅极晶体管中,栅极从四周包围沟道所在的区域,与平面晶体管相 比,全包围金属栅极晶体管的栅极对沟道的控制能力更强,能够更好的抑制短沟道效应。 全栅极纳米线可以在现有的替代栅鳍式场效应晶体管(FinTET)工艺流程中仅添 加两个过程模块得到,两个过程模块如下:一是在体硅(bulk Silicon)或者SOI wafer上生 长一层硅,这样可避免体硅材料漏电。二是在可更换的金属门回路上选择性的移除锗硅,然 后利用HKMG(high-k绝缘层 金属栅极)堆叠环绕硅通道去形成全包围金属栅极晶体管。

技术实现要素:

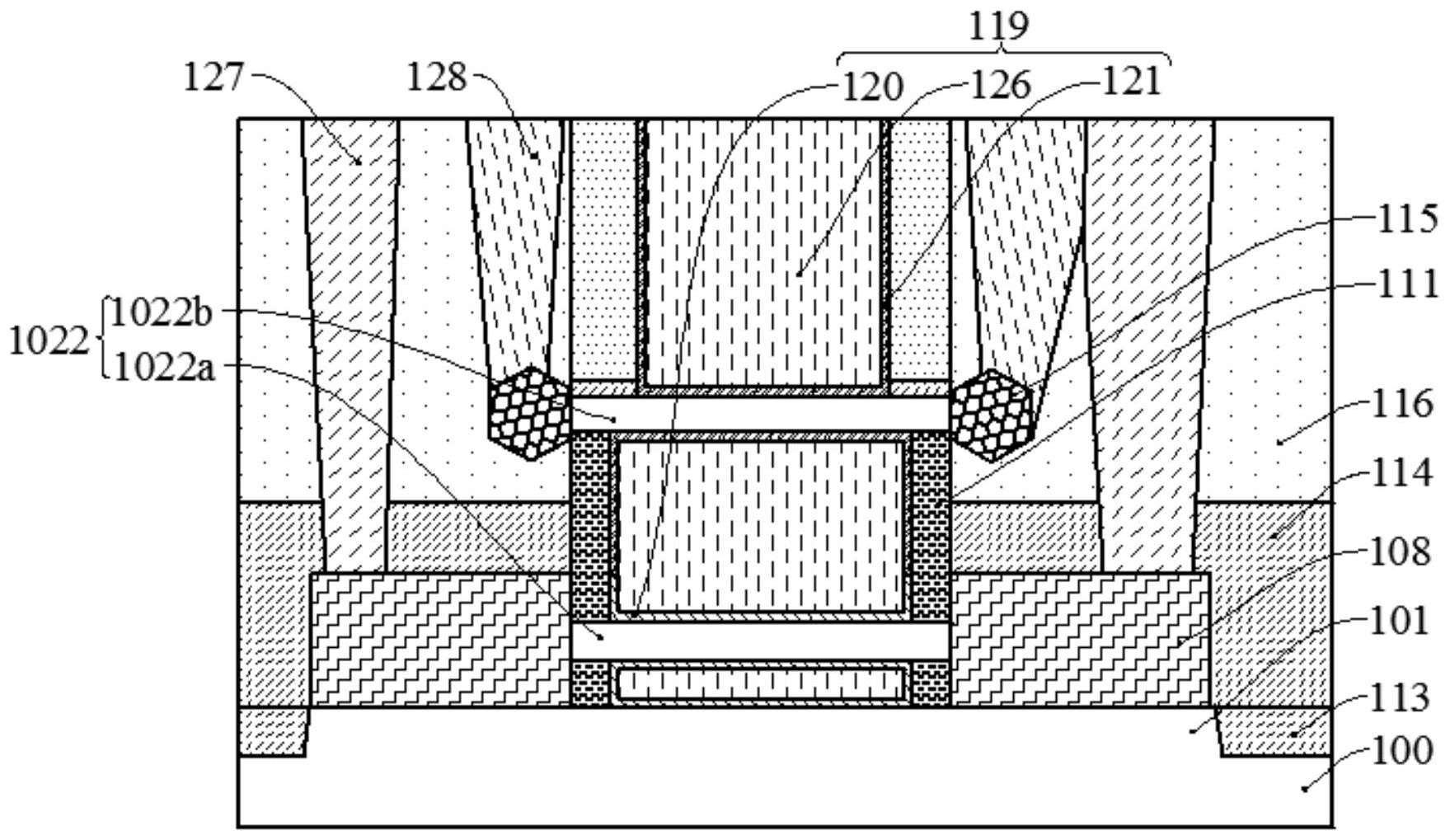

本发明实施例解决的问题是提供一种半导体结构及其形成方法,优化半导体结构 的电学性能。 为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基 底,所述基底包括衬底、凸出于所述衬底上分立的鳍部以及位于所述鳍部上的多个沟道叠 层,所述沟道叠层包括牺牲层和位于所述牺牲层上的沟道层,其中,靠近所述鳍部一侧的部 分所述沟道层作为第一沟道层,位于所述第一沟道层上的剩余所述沟道层作为第二沟道 层;形成横跨所述沟道叠层的伪栅结构,且所述伪栅结构覆盖所述沟道叠层的部分顶壁和 部分侧壁;在所述伪栅结构两侧的沟道叠层中形成第一源漏掺杂层,所述第一源漏掺杂层 与所述第一沟道层接触;在所述第二沟道层侧壁上形成第二源漏掺杂层;在所述伪栅结构 露出的衬底上形成层间介质层,所述层间介质层覆盖所述第一源漏掺杂层和第二源漏掺杂 层并露出所述伪栅结构顶部;去除所述伪栅结构,在所述伪栅结构的位置处形成栅极开口; 去除所述牺牲层,在所述牺牲层的位置处形成与所述栅极开口连通的通道;在所述栅极开 口和通道中形成栅极结构。 相应的,本发明实施例还提供一种半导体结构,包括:衬底;鳍部,位于所述衬底 上;第一源漏掺杂层,分立于所述鳍部上;一个或多个相间隔的第一沟道层,位于所述第一 5 CN 111613581 A 说 明 书 2/13 页 源漏掺杂层之间,且与所述第一源漏掺杂层接触,所述第一沟道层悬置于所述鳍部上方;第 二源漏掺杂层,分立悬空于所述第一源漏掺杂层上;一个或多个相间隔的第二沟道层,位于 所述第二源漏掺杂层之间,且与所述第一源漏掺杂层接触,所述第二沟道层悬置于所述第 一沟道层上方;栅极结构,横跨所述鳍部上的所述第一沟道层和第二沟道层,且包围所述第 一沟道层和第二沟道层。 与现有技术相比,本发明实施例的技术方案具有以下优点: 本发明实施例在鳍部上形成多个沟道叠层,所述沟道叠层包括牺牲层和位于所述 牺牲层上的沟道层,其中,靠近所述鳍部一侧的部分所述沟道层作为第一沟道层,位于所述 第一沟道层上的剩余所述沟道层作为第二沟道层,随后形成横跨所述沟道叠层且覆盖所述 沟道叠层的部分顶壁和部分侧壁的伪栅结构,在所述伪栅结构两侧的沟道叠层中形成第一 源漏掺杂层,在所述第二沟道层侧壁上形成第二源漏掺杂层,且在去除所述伪栅结构和牺 牲层后,在所述伪栅结构和牺牲层的位置处形成栅极结构。本发明实施例中,第一源漏掺杂 层、第一沟道层以及栅极结构中包围所述第一沟道层的部分栅极结构用于构成第一晶体 管,第二源漏掺杂层、第二沟道层以及栅极结构中包围第二沟道层的部分栅极结构用于构 成第二晶体管,从而通过上下堆叠的方式在所述栅极结构上形成不同晶体管,增加了半导 体结构的集成度,优化了半导体结构的电学性能。 附图说明 图1是一种半导体结构的结构示意图; 图2至图18是本发明实施例半导体结构的形成方法一实施例中各步骤对应的结构 示意图。