技术摘要:

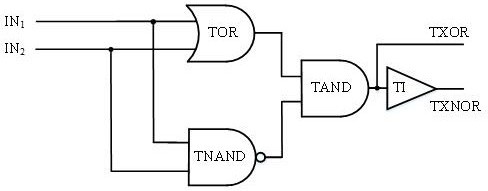

本发明公开了一种基于忆阻器的三值异或和同或逻辑门电路。本发明包括一个三值或门TOR,一个三值与门TAND,一个三值非门TI,一个三值与非门TNAND,利用忆阻器的开关特性和记忆特性实现,第一输入端IN1和第二输入端IN2分别为三值或门TOR和三值与非门TNAND的公共输入端, 全部

背景技术:

1971年,华裔科学家蔡少堂教授首次提出忆阻器的概念,2008年,惠普实验室研究 团队成功做出纳米忆阻器件,证实了蔡少堂教授的推断;并且进一步研究发现,忆阻器的非 易失型和纳米级尺寸有助于摩尔定律的延续,使得忆阻器能够同时计算和存储。 忆阻器的独特特性使其在模拟电路设计、非易失性存储、神经网络、数字逻辑等中 具有良好的应用前景,由于晶体管达到物理极限,忆阻器的开关行为的微小尺寸被推广为 基于晶体管的存储器的替代器件。 传统的数字系统是基于二进制数构建的,其中只考虑逻辑0和1;最近,多值逻辑的 概念成为一个共同的研究课题。1840年,英国的Thomas Fowler就以平衡三进制的设计,使 用木材建造了一台早期的计算机;1958年,苏联莫斯科国立大学由Nikolay Brusentsov建 造第一台数字电子三进制计算机Setun,它比二进制计算机在未来发展上更有优势。 三元数的主要优点是它比二进制数在相同的位数下所能携带更多的信息量,这降 低了互连和芯片面积的复杂性。随着元器件制造工艺技术的进步,为三进制逻辑电路的实 现提供了可能性。在20世纪80年代,基于使用增强和耗尽型晶体管的CMOS引入了第一个三 值逻辑门的实现。三进制逻辑电路非但比二进制逻辑电路速度更快、可靠性更高,还减少了 面积和互连的复杂性,且需要的设备功耗也更少。 忆阻器是实现三元系统的良好候选者,因为它可以处理两个以上的状态而无需使 用额外的硬件,可以进一步将其分为不同的量化级别到多级元素。实用的忆阻器与标准 CMOS技术兼容,这些忆阻器的尺寸在2-10nm范围内相对较小,使用忆阻器实现三元逻辑运 算为增强新颖的功能开辟了新的机会。

技术实现要素:

针对现有技术的不足,本发明提出了一种基于忆阻器的三值异或和同或逻辑门电 路。 本发明解决技术问题所采取的技术方案如下: 基于忆阻器的三值异或和同或逻辑门电路具体包括一个三值或门,一个三值与 门,一个三值非门,一个三值与非门。 三值或门电路由两个忆阻器构成。其中第一忆阻器M1正极作为第一输入端,第二 忆阻器M2正极作为第二输入端。第一忆阻器M1的负极与第二忆阻器M2的负极相连,并作为 输出端。对于三值或门,输出为两输入的最大值。 三值与门电路由两个忆阻器构成。其中第三忆阻器M3负极作为第一输入端,第四 忆阻器M4负极作为第二输入端。第三忆阻器M3的正极与第四忆阻器M4的正极相连,并作为 3 CN 111555751 A 说 明 书 2/3 页 输出端。对于三值与门,输出为两输入的最小值。 三值非门电路由两个忆阻器和两个NMOS管构成。其中第五忆阻器M5的负极与电源 VCC相连接,第五忆阻器M5的正极与第一NMOS管N1的漏极(D1)相连,并作为输出端。三值非门 的输入端与第一NMOS管N1的栅极(G1)、第二NMOS管N2的栅极(G2)相连。第一NMOS管N1的源 极(S1)与第二NMOS管的漏极(D2)、第六忆阻器M6的负极相连,第六忆阻器M6的正极接地,第 二NMOS管N2的源极(S2)接地。其中第一NMOS管N1的阈值导通电压为0.5V,第二NMOS管N2的 阈值导通电压为1.5V。对于三值非门,其中0的非逻辑为2,1的非逻辑为1,2的非逻辑为0。 三值与非门由一个三值与门和一个三值非门组成,在一个三值与门的输出端后连 接一个三值非门,即可得到的输出为逻辑与非。 本发明的有益效果:本发明结构清晰简单、易于实现。该门电路模型可用于多值数 字逻辑运算等诸多领域中的应用研究,具有重要意义。 附图说明 图1是本发明的基于忆阻器的三值异或和同或逻辑门电路框图。 图2是本发明的基于忆阻器的三值异或和同或逻辑门电路图。