技术摘要:

本发明公开了一种具有层次结构的集成电路的优化方法、系统及存储介质,所述集成电路的层次结构包括一个位于顶层的模块和多个位于其他层的模块,除了位于最低层的模块,每一模块都包括至少一个位于下一层的低层模块,所述方法包括:选择要进行优化的模块及所述模块中的 全部

背景技术:

集成电路的自动布局布线包括多个步骤。典型的自动布局布线工具首先将设计网 表划分为顶层设计和许多模块级设计,并且以DEF格式输出模块级电路。模块级电路的时序 约束条件由整个芯片电路的时序约束条件预算规划得到,包括模块的输入输出时序约束条 件和模块内部的时序约束条件,这些时序约束条件用SDF (Synopsys Design Constraint) 格式来描述,其中模块的输入输出时序约束条件包括最大输入时间约束、最小输入时间约 束、最大输出时间约束和最小输出时间约束。模块级的布局布线引擎将模块内部的层级结 构打平后对其进行最优布局布线,以期满足模块级的时序约束条件。然后将带有时序信息 和物理边界信息的所有模块的抽象表示进行整合,得到顶层设计。如果考虑到顶层设计的 RC提取后的时序分析,某一个模块的输入或(和)输出时序条件没有满足,也就是包括这个 模块的模块间时序路经不能满足时序约束条件,那么这个模块则处于关键路径上,在这种 情况下,对于处于关键路径上的所有模块,需要由顶层设计的时序约束条件重新预算规划 得到新的时序约束条件,并且这些模块的布局布线需要重新进行优化修改设计。这个过程 将反复迭代直至所有模块和模块间的时序约束条件都得到满足为止。 由上面的分析可知,在典型的自动布局布线工具中,电路被划分为顶层设计和模 块级设计。模块级设计的时序约束条件由顶层设计时序约束条件人为预算规划得到,在模 块级完成满足时序约束条件的布局布线后,被整合到顶层设计后,模块间时序约束条件可 能不满足,从而要反复迭代模块级布局布线过程,降低了整个流程的计算效率。

技术实现要素:

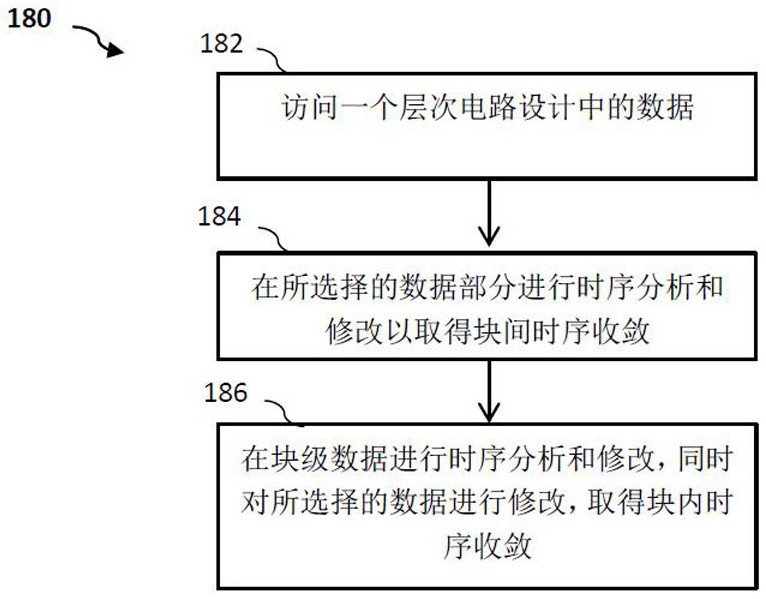

针对上述现有技术存在的问题,本发明提出一种具有层次结构的集成电路的优化 方法,在芯片级时序约束条件下对模块间的电路进行直接优化,从而有效提高自动布局布 线的效率。 本发明实施例中,提供了一种具有层次结构的集成电路的优化方法,所述集成电 路的层次结构包括一个位于顶层的模块和多个位于其他层的模块,除了位于最低层的模 块,每一模块都包括至少一个位于下一层的低层模块,所述方法包括: 选择要进行优化的模块及所述模块中的低层模块; 对所述低层模块间的边界路径进行时序分析和优化,使得所述模块中的电路满足所述 模块的时序约束条件。 本发明实施例中,通过对所述低层模块间的边界路径的网表、布线信息和电阻电 容信息进行时序分析和优化,来对所述低层模块间的边界路径进行时序分析和优化。 本发明实施例中,对所述低层模块间的边界路径进行时序分析和优化,包括: 4 CN 111611762 A 说 明 书 2/7 页 根据所述当前模块和所述低层模块的网表数据进行时序分析; 判断所述时序分析的结果是否满足对应的时序约束条件; 如果满足,则所述低层模块间的边界路径时序约束条件收敛; 如果不满足,则对所述低层模块间的边界路径进行时序优化。 本发明实施例中,通过插入缓冲器或改变逻辑门的大小来调整所述低层模块间边 界路径的时延。 本发明实施例中,对所述低层模块间的边界路径进行时序分析和优化之后,还包 括: 判断所述低层模块的内部路径是否满足时序约束条件,是则将优化后的边界路径数据 作为当前模块的时序收敛数据; 否则,对所述低层模块的内部路径进行时序优化,使得所述低层模块的内部路径满足 时序约束条件。 本发明实施例中,对所述低层模块的内部路径进行时序优化,使得所述低层模块 的内部路径满足时序约束条件之后,再次对所述低层模块间的边界路径进行时序分析和优 化,使得所述模块中的电路满足所述模块的时序约束条件。 本发明实施例中,对所述低层模块间的边界路径进行时序分析和优化,使得所述 模块中的电路满足所述模块的时序约束条件,包括: 获取所述模块的层次化RC信息; 将所述低层模块间的边界路径的RC信息进行合并,扩展到所述模块的整个边界路径以 产生所述模块的整个边界路径的RC信息; 对所述模块的整个边界路径的RC信息进行RC分析,来判定所述低层模块是否存在模块 内部的时序约束条件冲突; 如果所述低层模块存在模块内部的时序约束条件冲突,则对所述低层模块的内部路径 进行优化修改,使得所述低层模块的内部路径满足其相应的时序约束条件的同时,所述低 层模块间的边界路径的时序约束条件也得到满足。 本发明实施例中,对所述低层模块的内部路径进行时序优化,使得所述低层模块 的内部路径满足其相应的时序约束条件之后,再次对所述低层模块间的边界路径进行时序 分析和优化,使得所述模块中的电路满足所述模块的时序约束条件。 本发明实施例中,还提供了一种具有层次结构的集成电路的优化系统,其对具有 层次结构的集成电路进行优化时,采用上述的具有层次结构的集成电路的优化方法。 本发明实施例中,还提供了一种存储介质,所述存储介质中存储有计算机程序指 令,所述计算机程序指令被计算机执行时,执行上述的具有层次结构的集成电路的优化方 法。 与现有技术相比较,在本发明实施例所述层次电路优化方法中,首先由顶层设计 的时序约束条件直接得到模块间的时序约束条件,针对模块间的电路进行时序分析及优 化,得到满足模块间时序约束条件的电路布局布线实现,然后将模块间时序分析及优化修 改作为输入,即考虑模块间时序优化修改的影响下,进行模块内部的电路布局布线实现,同 时进行模块内部电路的时序分析及优化修改,根据模块内部电路的时序分析及优化修改的 结果,再考虑其对模块间电路时序分析的影响,由于模块内部电路的自动布局布线是在考 5 CN 111611762 A 说 明 书 3/7 页 虑模块间的时序分析及优化修改的前提下进行,因此能够减少模块级及顶层设计布局布线 的迭代次数,从而大大提高整个优化流程的计算效率。 附图说明 图1A为本发明实施例的集成电路的层次结构设计示意图; 图1B为本发明实施例的具有层次结构的集成电路的优化方法的流程图; 图2为本发明实施例的具有层次结构的集成电路的优化方法中取得模块间的时序收敛 的流程图; 图3A-3B为本发明实施例对模块的边界路径进行时序分析与优化的示例图; 图4为本发明实施例采用RC分析对模块的边界路径进行时序分析与优化的流程图; 图5A-5B为本发明实施例对模块的边界路径进行时序分析与优化的示例图; 图6为发明实施例的具有层次结构的集成电路的优化方法进行模块内部时序收敛的流 程图。