技术摘要:

公开了一种用于形成3‑D NAND器件的装置和方法。形成3‑D NAND器件的方法可包括形成插塞填充物和空隙。通过所述装置和方法获得的优点可包括较低的成本、较高的生产量、器件很少污染至无污染、蚀刻步骤期间很少损坏至无损坏、及结构完整性,以确保形成适当的氧化物‑氮 全部

背景技术:

NAND器件是例如可用于应用如闪存中的逻辑门。NAND器件的制造可包括在设置于 衬底上的层中形成沟道孔。然后可用牺牲材料填充沟道孔,并然后移除。图1A-1D中示意了 制造NAND器件100的工艺的一个实例。NAND器件100可包括衬底110、氮化物层120和氧化物 层130。根据需要重复氮化物层120和氧化物层130的沉积以形成堆叠。 如图1A中所示,NAND器件100包括第一堆叠140,其包含两个氮化物层120和两个氧 化物层130的交替。NAND器件100还包括第二堆叠150,其包含两个氮化物层120和两个氧化 物层130的交替。第一堆叠140和第二堆叠150可包含氮化物层120和氧化物层130的另外的 交替。 氮化物层120和氧化物层130经历蚀刻工艺以形成沟道孔,如图1B中所示。蚀刻工 艺可能涉及使用氟基物如NF3、CHF、SF6、CF4及其混合物的氧化物或氮化物干法蚀刻化学 品。在一些情况下,干法蚀刻化学品可能涉及氧气或臭氧。图1C示意了在经历第一工艺以形 成衬里、第二工艺以形成插塞填充物和第三抛光工艺后的NAND器件100,所述第一工艺在干 法蚀刻工艺以形成所谓的沟道孔或存储孔之后进行。NAND器件100然后包括衬里160和插塞 填充物170。衬里160可包含例如氧化硅(SiOx)。 插塞填充物170可包含多晶硅、钨(W)、氮化钛(TiN)、氧化铝(AlOx)、金属碳化物、 碳化钨(WC)、硼碳化钨(WBC)、金属氮化物或任何上文所列的组合。取决于用于插塞填充物 170的材料,可能会增加成本并因与集成有关的故障而增加不稳定性风险。插塞填充物170 可在堆叠140的底部处包含用来保护沟道孔或存储孔的牺牲材料。也可任选地在插塞填充 物170的顶部上设置盖(未示意)。例如,盖可包含金属氮化物,如氮化钛、氮化钨或氮化铝。 第三抛光工艺可以是化学机械抛光(CMP)。在第三抛光工艺之后,可在堆叠150、衬 里160和插塞填充物170的顶部上添加另外的氧化物-氮化物层堆叠。 然而,情况可能会是在用衬里160和插塞填充物170填充沟道孔后必须移除其孔中 作为牺牲材料的衬里160和插塞填充物170。可使用以下中的至少之一通过湿法蚀刻工艺移 除插塞填充物170:氢氧化铵(NH4OH)、过氧化氢(H2O2)、水(H2O)、HNO3、TDMH或前述的组合。例 4 CN 111599815 A 说 明 书 2/5 页 如,可使用卤化物化学品如氢氟酸(HF)、盐酸(HCl)或氢溴酸(HBr)通过干法蚀刻移除插塞 填充物170。可在湿法清洁工艺后用HF混合物来移除衬里(160)。 图1D示意了在进行移除之后的NAND器件100。然而,化学方法可能因用于移除衬里 160和/或插塞填充物170的化学品而对氮化物层120或氧化物层130留下残余物180和/或引 起损坏190。残余物180和损坏190可能使得NAND器件100不可用。另外,衬里160和插塞填充 物170的移除可以缓慢的蚀刻速率进行,这意味着移除衬里160和插塞填充物170的时间可 能不期望地长。例如,这可能是由重结晶硅或(111)结晶取向的硅形成的插塞填充物170的 结果。重结晶硅可能因在形成另外的堆叠时的退火工艺而产生。 此外,可能出现的另一个问题是当在第一堆叠140和第二堆叠150的顶部上设置另 外的堆叠时堆叠未对齐。未对齐可能是在制造期间施加于不同的堆叠、衬里160和/或插塞 填充物170上的应力的结果。 因此,期望取得一种用于以低成本和高生产量形成NAND器件的装置和方法,其在 沟道孔中的残余物极少或无残余物且无损坏并具有良好的结构完整性。

技术实现要素:

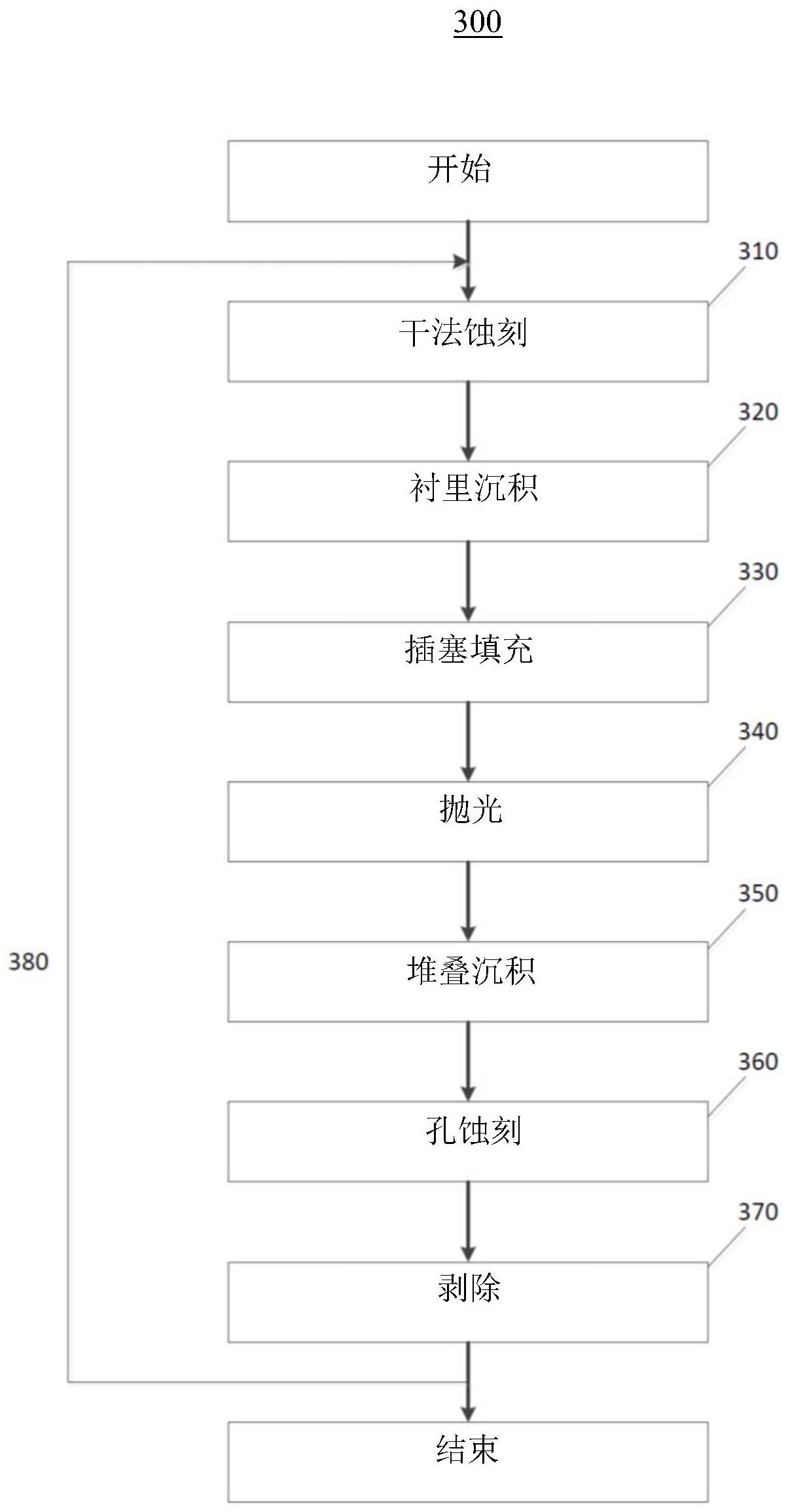

提供本概述是为了以简化的形式引入一系列概念。下文在本公开的实例实施例的 详细描述中更详细地描述这些概念。本概述不打算标识所要求保护的主题的关键特征或必 要特征,也不打算用于限制所要求保护的主题的范围。 根据本发明的至少一个实施方案,公开了一种方法,所述方法包括在衬底上形成 3-D NAND器件的方法。在各种实施方案中,所述方法可包括:在半导体衬底上沉积双层结 构,其中所述双层结构包含氧化物层和氮化物层的交替层;用第一化学品在所述双层结构 中蚀刻沟道孔;在双层结构的顶部上和/或在沟道孔内双层结构的侧面上沉积衬里;在沟道 孔中沉积插塞填充物,所述插塞填充物包含空隙及硅锗插塞或缓变锗插塞中的至少之一; 抛光所述插塞填充物;用第二化学品蚀刻所述插塞填充物;和/或移除所述衬里;其中重复 任何上述步骤以形成所需高度的3-D NAND器件。 附图说明 下文将参照某些实施例的图式来描述本文中所公开的本发明的这些和其它特征、 方面和优势,所述实施例意图说明而不是限制本发明。 图1A-1D为通过现有技术工艺形成的NAND器件的横截面图示。 图2A-2I为根据至少一个本发明实施方案形成的NAND器件的横截面图示。 图3为根据至少一个本发明实施方案的工艺流程图。 图4为根据至少一个本发明实施方案形成的NAND器件的横截面图示。 应了解,图中的元件是为了简单和清晰而示出的,且不一定按比例绘制。举例来 说,图中的一些元件的尺寸可能相对于其他元件夸大,以有助于改进对本公开所说明实施 例的理解。