技术摘要:

本发明公开了一种用于激光雷达的DDR4内存,包括控制芯片和若干内存单元,控制芯片与内存单元电连接,地址信号通路中,一个内存单元通过第一带状线与第一端接电阻相连接,第一带状线与所述第一端接电阻的阻值相同,差分时钟信号通路中,一个内存单元通过一组第二带状线 全部

背景技术:

随着智能网联技术的进步,自动驾驶汽车逐步在市场上开始普及。在高级别的自 动驾驶汽车中,激光雷达是一种重要的传感器。激光雷达通过向目标物体发射一束激光,而 后根据接收和反射的时间差来确定目标物体的距离,并且根据距离以及激光发射的角度, 推导出物体的位置信息。在实际使用过程中,激光雷达收集到的所有反射点坐标的集合称 之为点云。通常16线的激光雷达每秒要处理的点为30万个;32线的激光雷达每秒要处理的 点为70万个;64线的激光雷达每秒要处理的点为220万个。 需要处理点云数据时,需要通过FAKRA接插件引入到激光雷达控制器中,FPGA将需 要处理的点云数据从DDR4中读出,而后进行处理。从原始的距离信息到实际物体的坐标信 息,至少要涉及4次浮点运算和3次三角函数运算。由于点云数据量巨大,所以如果主芯片算 力不够,或者DDR4数据传输速率等条件不能满足要求,就会导致激光雷达处理帧率无法满 足设计指标。

技术实现要素:

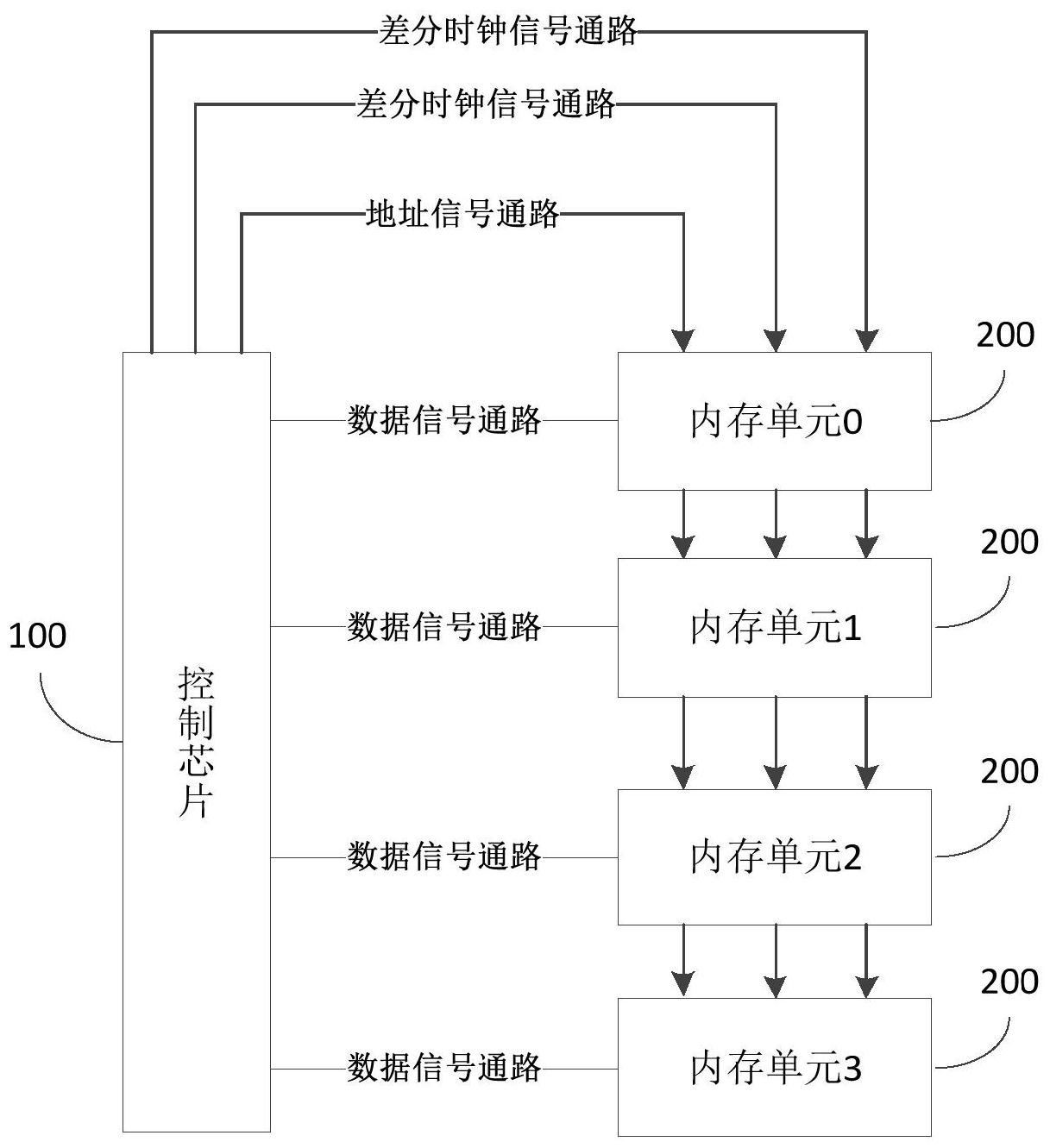

本发明提供一种用于激光雷达的DDR4内存,以达到使DDR4满足激光点云数据处理 的数据读写速率要求;提高DDR4 PCB的信号传输特性的目的。 本发明实施例提供了一种用于激光雷达的DDR4内存,包括控制芯片和若干内存单 元,所述控制芯片与所述内存单元电连接, 地址信号通路中,一个内存单元通过一组第一带状线与第一端接电阻相连接,所 述第一带状线与所述第一端接电阻的阻值相同, 差分时钟信号通路中,一个内存单元通过一组第二带状线与所述控制芯片相连 接,一个内存单元通过一组第三带状线与二端接电阻以及第三端接电阻相连接,每两个内 存单元之间通过一组第四带状线相连接, 其中,所述第二带状线与所述第三带状线的阻值相同,所述第二端接电阻与所述 第三端接电阻的阻值相同。 进一步的,所述控制芯片、内存单元配置在PCB的顶层,所述第一端接电阻、第二端 接电阻以及第三端接电阻配置在所述PCB的底层, 所述第一带状线、第二带状线、第三带状线以及第四带状线配置在所述PCB的信号 层,所述第一带状线、第二带状线、第三带状线通过过孔接入所述顶层和底层,所述第四带 状线通过过孔接入所述顶层。 进一步的,所述PCB采用16层结构,从顶到底依次为: 顶层、第一地层、第一信号层、第二地层、第二信号层、第三地层、第三信号层、电源 层、第四地层、第四信号层、第五地层、第五信号层、第六地层、第六信号层、第七地层、底层, 4 CN 111581134 A 说 明 书 2/6 页 其中,所述第二带状线、第三带状线以及第四带状线布置在同一层信号层中。 进一步的,每层地层以及电源层均通过负片工艺制成。 进一步的,所述16层结构中,每相邻的两层之间交替的配置半固化片以及芯板。 进一步的,布置在同一信号层中的每两根所述第一带状线的间距为介质层厚度的 3倍, 所述介质层为,与该信号层对应的地层配置的半固化片或者芯板。 进一步的,所述第一带状线配置在所述第二信号层。 进一步的,所述第二带状线、第三带状线以及所述第四带状线配置在所述第一信 号层。 进一步的,数据信号通路中,内存单元通过一组第五带状线与所述控制芯片的数 据端口相连接,通过一组第六带状线与所述控制芯片的数据片选端口相连接,通过一组第 七带状线与所述控制芯片的数据掩码端口相连接, 所述第五带状线、第六带状线以及第七带状线配置在所述第一信号层,所述第二 带状线、第三带状线以及所述第四带状线与所述第五带状线、第六带状线以及第七带状线 的间距至少为介质层厚度的3倍, 所述介质层为,与第一信号层对应的地层配置的半固化片或者芯板。 进一步的,所述第五带状线与所述第七带状线的阻值相同。 与现有技术相比,本发明的有益效果在于:本实施例中,对DDR4 PCB中的地址信号 通路、时钟信号通路以及数据信号通路部分进行重新设计,提出了一种针对上述信号通路 中带状线的走线拓扑结构以及带状线与端接电阻之间的阻抗匹配方式,可以使DDR4满足激 光点云数据处理的数据读写速率要求,同时,也可以提高DDR4 PCB的信号传输特性。 附图说明 图1是实施例中的内存整体结构框图; 图2是实施例中的地址信号通路结构示意图; 图3是实施例中的差分时钟信号通路结构示意图; 图4是实施例中的数据信号通路结构示意图; 图5是实施例中的PCB层级结构示意图; 图6是实施例中的测试结果图A; 图7是实施例中的测试结果图B; 图8是实施例中的测试结果图C。