技术摘要:

公开了用于形成硅化物膜的方法。公开了在被进一步处理以形成硅化物膜的硅表面上选择性地沉积含金属膜的方法。本公开的具体的实施方式涉及在FinFET结构上形成硅化物膜而不在电介质上形成金属层。

背景技术:

鳍式场效应晶体管,也被称为FinFET,是在现代处理器设计中使用的一种类型的 非平面或三维晶体管。就像在更早前的平面设计中一样,FinFET典型地构建在SOI(绝缘体 上硅)基板上。然而,FinFET设计还使用了上升到绝缘体的水平上方的导电通道,从而形成 形状像鳍的薄硅基结构,它被称为栅电极。此鳍状电极允许多个栅极在单个晶体管上操作。 与主流CMOS技术相比,FinFET器件还具有显著更快的切换时间和更高的电流密度。 持续存在对新的FinFET设计的需要。具体地,存在对新的材料和表面组合物的需 要以允许一组扩展设计选项。选择性沉积已经展示出是有前景的,因为它具有允许在选择 表面上沉积膜并简化集成方案的潜力。 材料的选择性沉积可以以多种方式完成。例如,一些工艺可只基于表面的表面化 学物质而具有对该表面的固有选择性。这些工艺极其少见并通常需要具有极为不同的表面 能的表面,诸如金属和电介质。在FinFET中以及在表面类似(例如,SiO2对SiN)的其他情况 下,需要通过采用与一个表面选择性地反应而不与其他表面选择性地反应的表面处理来选 择性地阻挡表面,从而在后续沉积工艺期间有效地阻止任何表面反应。然而,一些沉积前驱 物没有通过当前技术被有效地阻挡。 因此,本领域中持续存在对抑制在某些表面上的沉积而在其他表面上选择性地沉 积膜的方法和材料的需要。

技术实现要素:

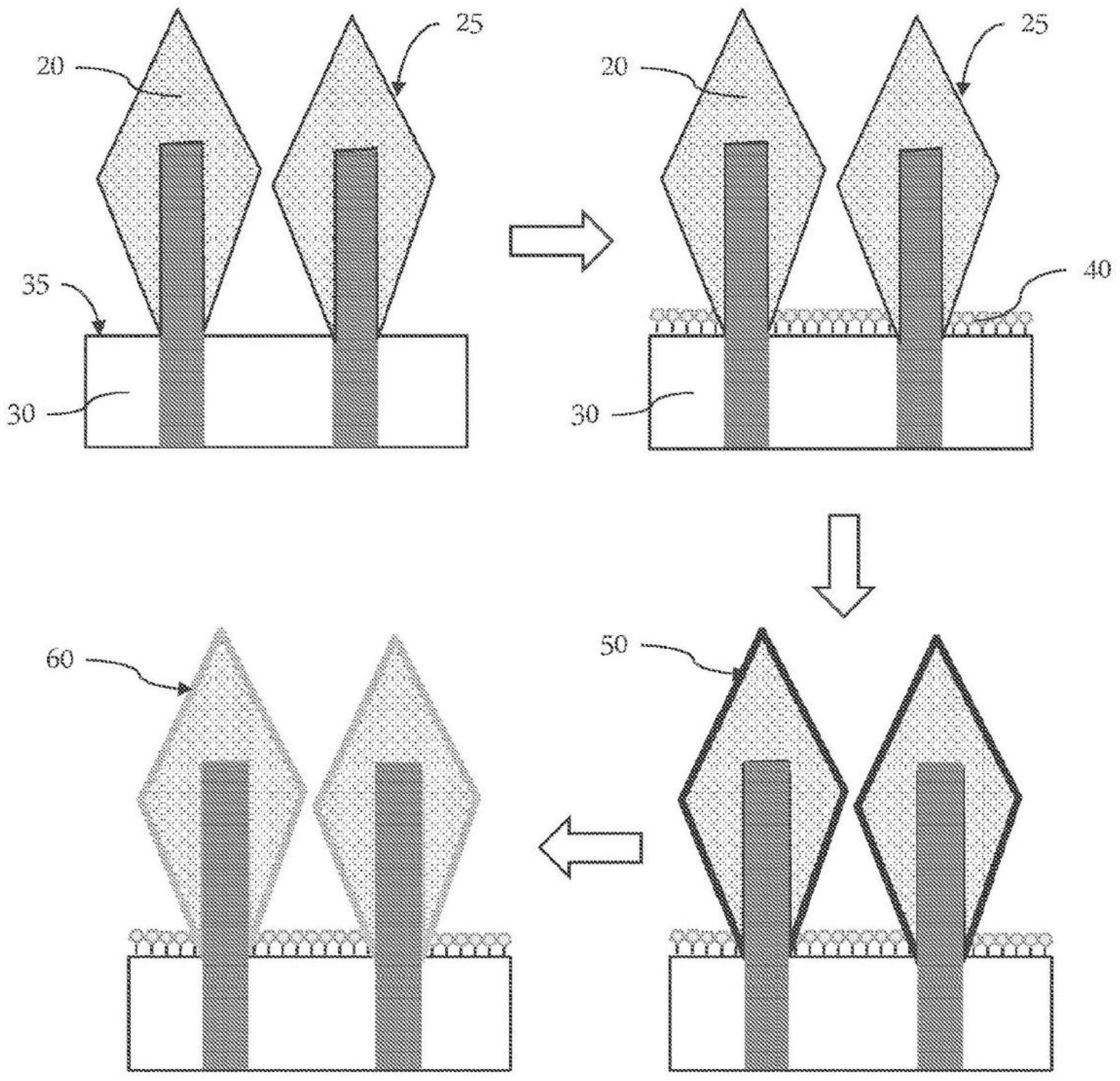

本公开的一个或多个实施方式针对一种基板处理方法,包括提供基板,所述基板 包括第一半导体表面和第二电介质表面。将所述基板暴露于阻挡化合物以相对于所述第一 表面在所述第二表面上选择性地形成阻挡层。将所述基板暴露于钛前驱物以相对于所述第 二表面在所述第一表面上选择性地沉积含Ti层。加热所述基板以形成包含钛和硅的经改性 的第一表面。 本公开的附加的实施方式针对一种基板处理方法,包括提供基板,所述基板包括 第一半导体表面和第二电介质表面。将所述基板暴露于阻挡化合物以在所述第二表面上选 择性地形成阻挡层。将所述基板暴露于钛前驱物以相对于所述第二表面在所述第一表面上 选择性地沉积含Ti层。将所述基板暴露于锗前驱物以相对于所述第二表面在所述第一表面 上选择性地沉积含Ge层。加热所述基板以形成包含钛、锗和硅的经改性的第一表面。 本公开的进一步实施方式针对一种基板处理方法,包括提供基板,所述基板包括 第一硅表面和第二氧化硅表面。将所述基板暴露于阻挡化合物以在所述第二表面上选择性 地形成阻挡层。将所述基板暴露于钛前驱物以相对于所述第二表面在所述第一表面上选择 3 CN 111602228 A 说 明 书 2/7 页 性地沉积含Ti层。将所述基板暴露于硅前驱物以相对于所述第二表面在所述第一表面上选 择性地沉积含Si层。加热所述基板以形成基本上由TiSi2组成的经改性的第一表面。 附图说明 以能够详细地理解本公开的上述特征的方式,可参考实施方式来对上文简要概述 的本公开进行更具体的描述,其中一些在附图中示出。然而,应注意,附图仅示出了本公开 的典型的实施方式并因此不应视为对本公开的范围的限制,因为本公开可允许其他等效实 施方式。 图1示出了根据本公开的一个或多个实施方式的选择性沉积工艺;以及 图2示出了根据本公开的一个或多个实施方式的用于在半导体表面上选择性地沉 积含钛层的示例性工艺顺序。 在附图中,类似部件和/或特征可具有相同附图标记。进一步地,相同类型的各种 部件可通过在附图标记后加上区分类似部件的划线和第二标记来区分。如果在本说明书中 仅使用了第一附图标记,那么不管第二附图标记如何,所述描述适用于具有相同第一附图 标记的类似部件中的任一个。